current location :home>News

Recently, the IEEE International Solid-State Circuits Conference (ISSCC 2025) was held in San Francisco, USA. Organized by the IEEE Solid-State Circuits Society (SSCS), ISSCC is widely recognized by both global academia and industry as the premier conference in the field of integrated circuit design, often referred to as the "Olympics of Chip Design." Established in 1953, ISSCC has historically served as the launchpad for the world's most cutting-edge solid-state circuit technologies, attracting over 3,000 participants from industry and academia worldwide each year.

Each accepted paper at ISSCC represents the most advanced research results in the current chip domain. This year, the School of Microelectronics at the Southern University of Science and Technology (SUSTech) had two papers accepted: Paper 1, *"A 112Gb/s 0.61pJ/b PAM-4 Linear TIA Supporting Extended PD-TIA Reach in 28nm CMOS,"* and Paper 2, *"A 100Gbaud 4Vppd Distributed Linear Driver with Cross-folded Transmission Lines and Cross-coupled Gm Cells for Built-in 5-tap FFE in 130nm SiGe BiCMOS."* To date, SUSTech has published a total of 8 papers at ISSCC as the primary affiliation, 5 of which come from Professor Quan Pan's team.

Group photo of the team's students at ISSCC

Live presentation scene

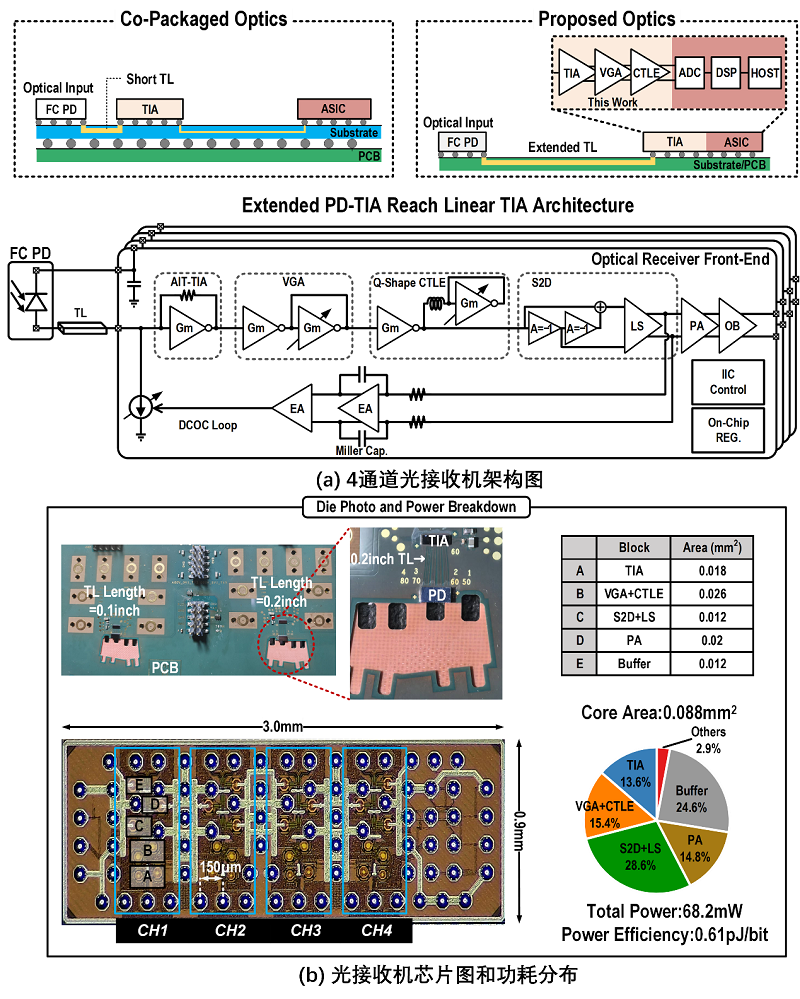

Paper 1 Introduction: *A 112Gb/s 0.61pJ/b PAM-4 Linear TIA Supporting Extended PD-TIA Reach in 28nm CMOS*

The continuous growth in demand for cloud storage and AI applications is driving optical communication technologies toward higher data rates and lower costs. Co-packaging a photodetector (PD) and a BiCMOS transimpedance amplifier (TIA) with a CMOS switch ASIC on the same substrate can effectively improve signal integrity, reduce power consumption, increase integration density, and lower costs. Integrating the TIA within the switch ASIC in CMOS technology can further reduce the total component count, achieving even lower cost and power consumption. To ensure thermal expansion compatibility of the ASIC, optical coupling flexibility, mechanical stability, and to avoid field replacement issues caused by excessively short PD-TIA distances, while further increasing the interconnect bandwidth density of the optical interface, the PD-to-TIA+ASIC distance needs to be properly designed. However, increasing the PD-TIA distance leads to increased signal reflections, degraded in-band amplitude flatness, and reduced bandwidth.

Addressing both system architecture and circuit design, the team proposed a 4×112Gb/s PAM-4 TIA featuring an active-input termination TIA (AIT-TIA), a Q-peaking continuous-time linear equalizer (CTLE), and a signal-interpolating single-ended-to-differential converter (S2D) for extended PD-TIA reach scenarios. This TIA achieves an energy efficiency of 0.61 pJ/b and supports a PD-TIA distance of 0.2 inches, reaching the longest distance among all types of optical receivers reported to date.

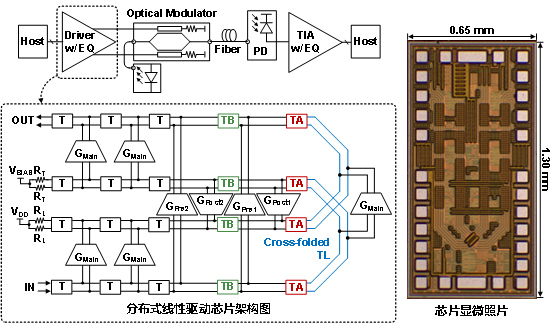

Paper 2 Introduction: *A 100Gbaud 4Vppd Distributed Linear Driver with Cross-folded Transmission Lines and Cross-coupled Gm Cells for Built-in 5-tap FFE in 130nm SiGe BiCMOS*

For linear direct-drive pluggable optical links, Professor Quan Pan's team at SUSTech designed a linear driver chip for optical modulators. The team proposed a distributed topology based on cross-coupled active cells and cross-folded transmission lines. On one hand, it utilizes the parasitic inductance of the transmission lines to neutralize the parasitic capacitance from high-swing active transconductance cells, thereby achieving high bandwidth. On the other hand, it introduces five amplification paths with different delays between the input and output ports of the driver chip, realizing a built-in 5-tap feed-forward equalizer (FFE) and enhancing the driver chip's equalization capability.

These two works were supported by the National Key R&D Program of China and the National Natural Science Foundation of China (NSFC).

Furthermore, at this conference, Ph.D. students Liping Zhong and Fuzhan Chen from the team received the IEEE Solid-State Circuits Society (SSCS) 2024-2025 Predoctoral Achievement Award. This marks the first time SUSTech has received this award. The award recognizes the most outstanding doctoral students worldwide in the field of integrated circuit design for the given year. Both students, as the first batch of Ph.D. graduates from the team, have entered academic positions at universities.

Liping Zhong's award certificate

Fuzhan Chen's award certificate

It is noted that this award was established in 1983, initially with one recipient per year, and is presented annually in mid-February at the ISSCC conference in San Francisco. It is the highest global academic honor bestowed upon doctoral students in the field of integrated circuit design. The award selection committee comprises renowned experts from both international industry and academia, and the evaluation process is highly rigorous, comprehensively assessing candidates based on the technical novelty, industrial application value, and academic impact of their research achievements. According to public reports, since 1983, fewer than 10 doctoral students from Mainland China have received this honor, hailing from Tsinghua University, Peking University, Fudan University, and the University of Electronic Science and Technology of China (UESTC).

This prestigious honor represents a high level of recognition for the international competitiveness of SUSTech's School of Microelectronics in the field of solid-state circuit research. In the future, the School will continue to strive to cultivate more research talents with global vision and academic potential, contributing to the advancement of the discipline and technological innovation.

Paper Information:

[1] Y. Zhang, Y. Yao, W. Zhou, X. Luo, Z. Li, D. Zhan and Q. Pan, "A 112Gb/s 0.61pJ/b PAM-4 Linear TIA Supporting Extended PD-TIA Reach in 28nm CMOS", in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2025.

[2] F. Chen, C. Patrick Yue and Q. Pan, "A 100Gbaud 4Vppd Distributed Linear Driver with Cross-Folded Transmission Lines and Cross-Coupled Gm Cells for Built-in 5-Tap FFE in 0.13μm SiGe BiCMOS ", in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2025.