current location :home>News

Recently, the team led by Professor Quan Pan at the National Demonstration School of Microelectronics, College of Engineering, Southern University of Science and Technology (SUSTech), has achieved significant progress in high-speed communications and optoelectronic integrated circuit design. Two of their works have been accepted for presentation at the IEEE International Solid-State Circuits Conference (ISSCC), and one paper has been accepted at the Optical Fiber Communication Conference (OFC). The accepted works include a high-energy-efficiency chiplet-interconnect simultaneous bi-directional transceiver chip, a high-energy-efficiency high-speed chiplet-interconnect and memory interface chip, and a monolithic integrated high-speed optical receiver chip.

Furthermore, Professor Pan’s team published two papers in the prestigious IEEE Transactions on Circuits and Systems I: Regular Papers (IEEE TCAS-I). These papers report a receiver featuring a current-reuse analog front-end (AFE) and a single-loop half-rate reference-less clock and data recovery (CDR), and a single-ended receiver front-end with crosstalk cancellation and signal reutilization. Notably, the paper on crosstalk cancellation and signal reutilization was selected as a highlight paper for the January 2026 issue of IEEE TCAS-I.

ISSCC is widely recognized by both academia and industry as the premier conference in the field of integrated circuit design, often referred to as the "Olympics of Chip Design." Established in 1953, it has historically served as the launchpad for the world's most cutting-edge IC technologies, attracting over 3,000 participants from global industry and academia each year. Each accepted paper represents the most advanced research results in the chip domain. The titles of the two papers from Professor Quan Pan’s group accepted by ISSCC this year are: *“A 72Gb/s/pin Single-Ended Simultaneous Bi-Directional Transceiver with C-Peaking Leakage Cancellation and Dual-Loop Hybrid Impedance Calibration for Chiplet Interfaces”* and *“A 72Gb/s/pin Single-Ended Driver-Cooperative Coded PAM3 Transceiver with Asymmetric Data-Dependent Equalization and Bias-Peaking for Chiplets and Memory Interfaces,”* with the latter being selected as a Highlighted Paper.

OFC, jointly organized by Optica, the IEEE Communications Society (ComSoc), and the IEEE Photonics Society (LEOS), is the largest and most influential premier academic and industrial event in the global optical communications field. Founded in 1975, OFC has over 50 years of history and is recognized as the benchmark for the optical communications industry, attracting over 16,000 attendees and more than 600 exhibitors annually, serving as a vital platform for product launches, collaboration, and future insights. Each accepted paper at OFC represents a critical development direction in optical communications. The title of the paper from Professor Pan’s group accepted by OFC this year is: *“A Monolithic CMOS 28Gb/s PAM-4 Optical Receiver Front-End with Lateral-Enhanced P-Well/N-Well APD for VCSEL-Based Links.”* This work was selected as a Top-Scored paper and has received an invitation for submission to the Journal of Lightwave Technology (JLT).

Figure 1: On-site presentation photo at ISSCC

Paper 1: High-Efficiency Chiplet-Interconnect Simultaneous Bi-Directional Transceiver Chip

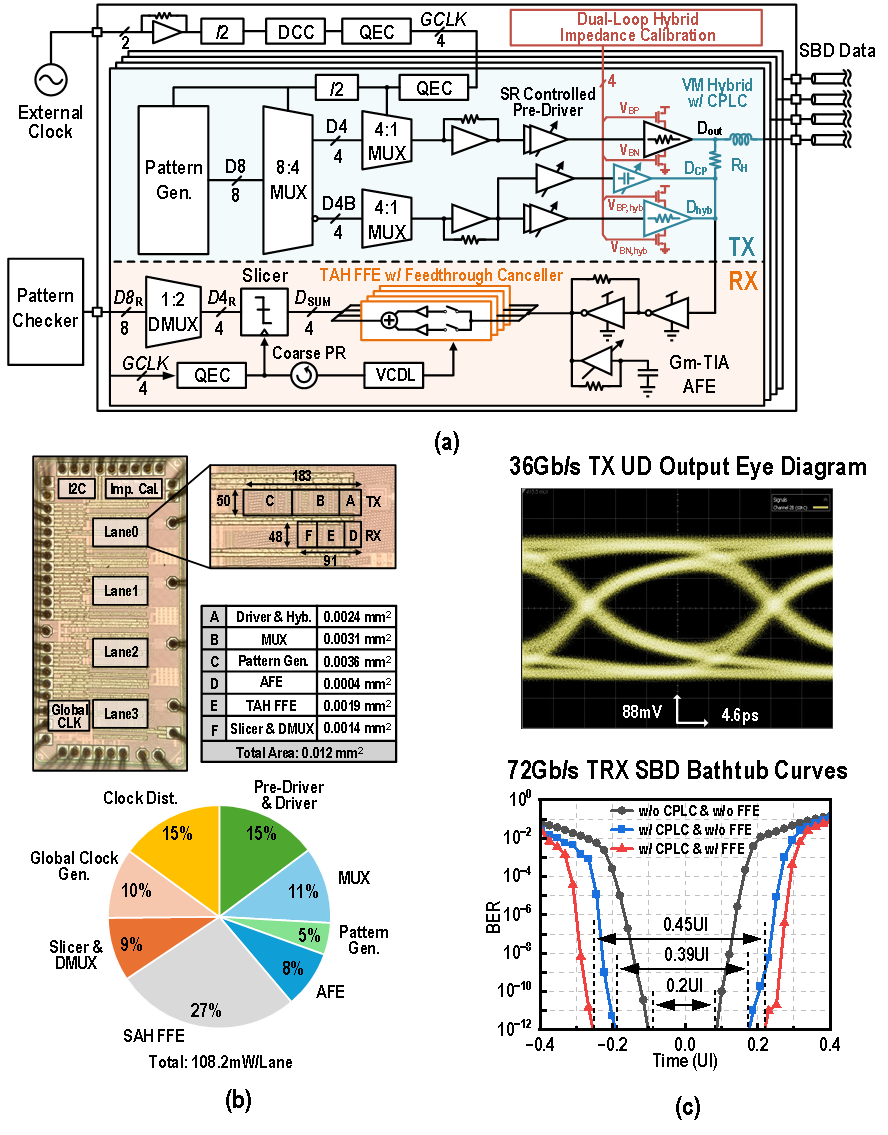

The explosive growth of artificial intelligence has accelerated the development of high-performance computing and high-bandwidth interconnects. To continuously increase the data throughput of interconnect interfaces, simultaneous bi-directional (SBD) links show the potential to double system throughput by transmitting and receiving data simultaneously on the same channel. However, the design of high-speed SBD links faces challenges from high-frequency leakage of outbound signals and the precision of the inbound/outbound signal decoupling coefficient. To address these technical hurdles, the SUSTech team proposed a 72 Gb/s/pin SBD transceiver chip featuring two key technologies: First, a C-peaking leakage cancellation technique that extracts and feeds forward an inverted high-frequency leakage component, reducing the high-frequency leakage amplitude from 148mV to 55mV (a suppression of ~63%) and achieving a 6-fold improvement in eye opening amplitude. Second, a dual-loop impedance calibration technique that enables the hybrid driver impedance to track variations in both the main driver and the channel, thereby improving the cancellation accuracy of the outbound signal. When the channel impedance varies by 20%, this dual-loop calibration reduces the residual error from a maximum of 60mV to below 5mV, a reduction of approximately 92%. Measurement results show that, using the proposed techniques combined with receiver FFE, the transceiver chip achieves an error-free interval of 0.45UI at 72 Gb/s, with the receiver eye height increased to approximately 244mV and overall energy efficiency reaching 1.5 pJ/b, demonstrating its competitiveness for high-bandwidth-density chiplet interfaces.

Figure 2: Circuit architecture diagram, power breakdown chart, and measurement results of the simultaneous bi-directional transceiver chip.

Ph.D. student Xuxu Cheng is the first author of the paper. Professor Quan Pan is the sole corresponding author, and the School of Microelectronics at SUSTech is the sole affiliated institution. This work was supported by the Shenzhen Science and Technology Program.

Paper 2: High-Efficiency High-Speed Chiplet-Interconnect and Memory Interface Chip

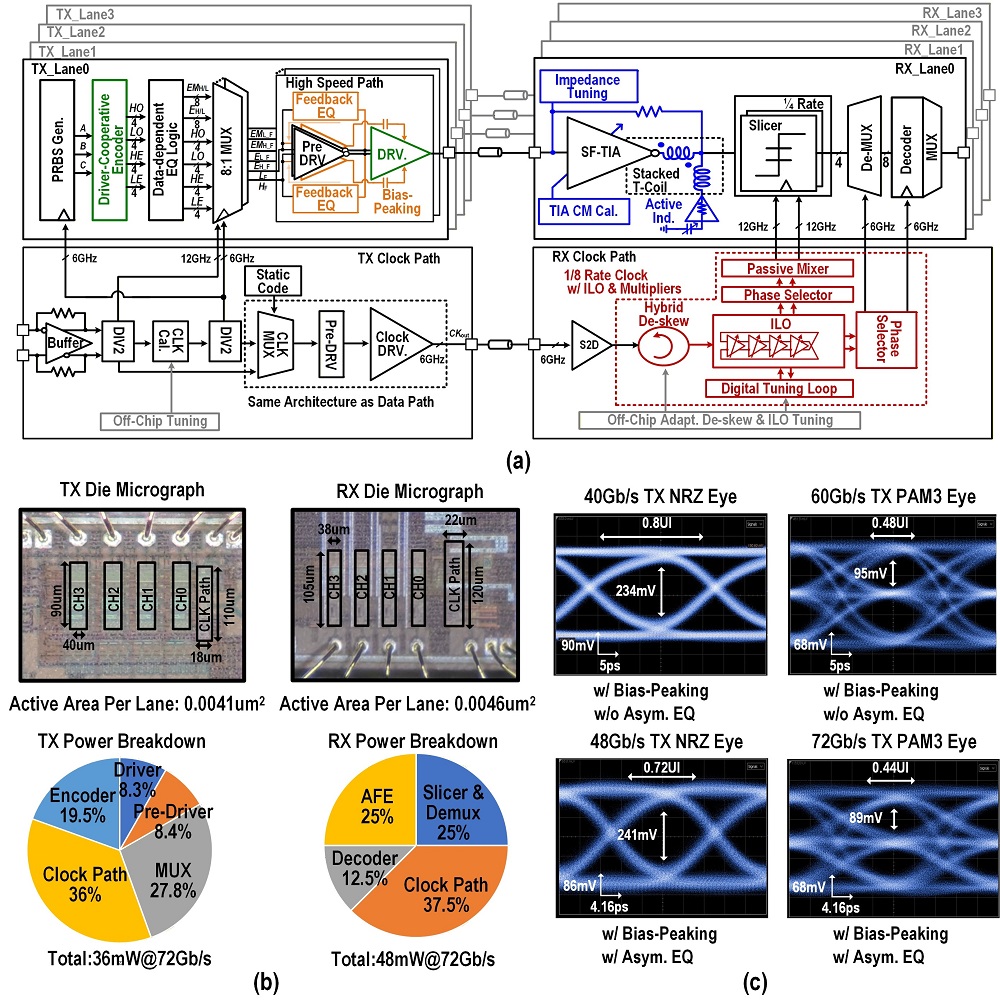

With the rapid development of AI and cloud computing applications, chiplet interconnects and memory interfaces require higher data throughput under limited power budgets, driving the continuous evolution of high-speed, low-power single-ended wireline transceivers. Recently, PAM3 signaling has emerged as a promising candidate for next-generation high-density short-reach interconnects due to its 1.5× bandwidth efficiency compared to NRZ and better noise and crosstalk tolerance than PAM4. However, PAM3 signals are more sensitive to inter-symbol interference (ISI), and switching jitter between different transition edges can lead to eye width contraction and signal integrity degradation. To address this, the SUSTech team proposed a 72 Gb/s/pin single-ended PAM3 transceiver for chiplet and memory interfaces. The design employs driver-cooperative coding and impedance-calibrated TIA termination co-optimization, improving signal integrity while reducing signaling power by 46%. Furthermore, asymmetric data-dependent equalization and bias-peaking techniques effectively mitigate ISI and switching jitter for different PAM3 edges, enhancing eye areas by 1.9× and 2.8×, respectively. Additionally, the paper presents a 1/8-rate forwarded-clock frequency doubling scheme enabling low-power, wide-range deskew operation. Fabricated in 28nm CMOS, the transceiver achieves a data rate of 72 Gb/s/pin with energy efficiencies of 0.7 pJ/b and 1.17 pJ/b at 48 Gb/s and 72 Gb/s, respectively, showcasing its potential for next-generation high-bandwidth, low-power memory and chiplet interconnect systems.

Figure 3: Circuit architecture diagram, chip micrograph, power breakdown chart, and measurement results of the memory interface chip.

Postdoctoral Fellow Hongzhi Wu is the first author of the paper. Professor Quan Pan is the sole corresponding author, and the School of Microelectronics at SUSTech is the sole affiliated institution. This work was supported by the National Natural Science Foundation of China (NSFC) and the Shenzhen Science and Technology Program.

Figure 4: Screenshot/record of the online presentation

Paper 3: Monolithic Integrated High-Speed Optical Receiver Chip

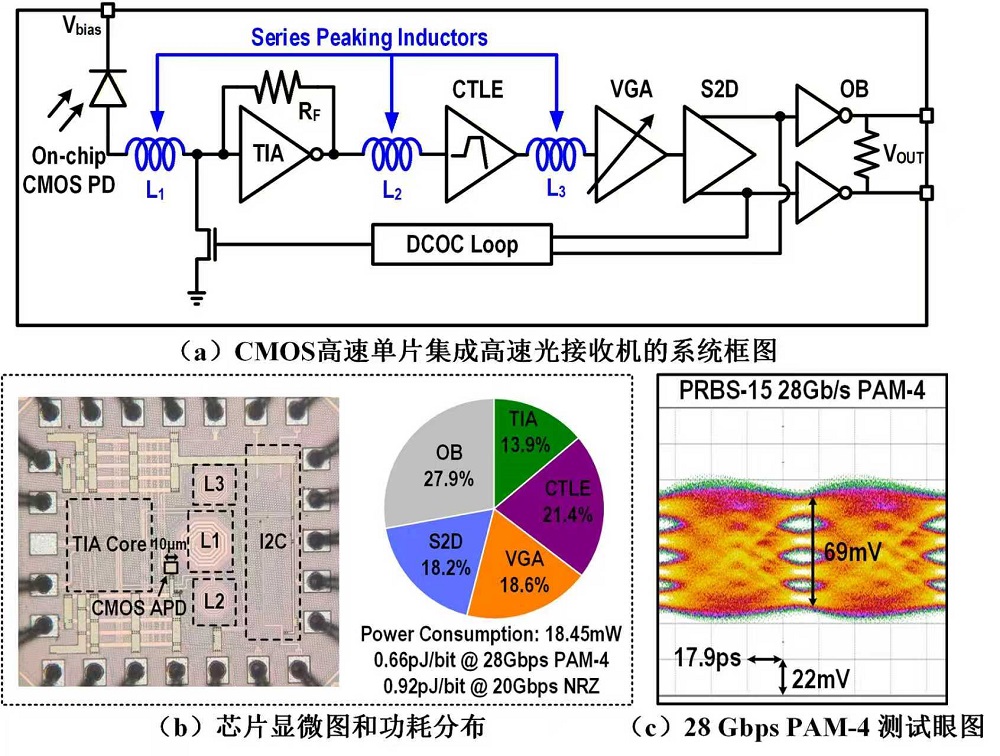

In recent years, Vertical-Cavity Surface-Emitting Lasers (VCSELs) operating at 850 nm have been widely adopted in data centers due to their high-bandwidth connectivity. Emerging Co-Packaged Optics (CPOs) utilizing VCSEL technology can further address scalability and power consumption challenges in heterogeneous integrated optical modules. To reduce packaging complexity and cost for corresponding optical modules, the industry is adopting CMOS on-chip photodetectors (PDs) in optical receiver front-ends as a replacement for III-V PDs. This approach shortens the transmission distance from the optical device to the transimpedance amplifier circuit, avoids packaging parasitic effects, and enables full integration of the optical device with the ASIC. However, the main performance bottleneck for such fully integrated receiver systems remains the responsivity and bandwidth of the CMOS PD, which significantly limits system speed and bit error rate (BER).

Tackling both the optical device and receiver front-end circuit, the team implemented a 28 Gb/s PAM-4 receiver for VCSEL-based optical links in 28-nm CMOS. This chip integrates the PD and TIA circuit on a single die, achieving a monolithic integration scheme using standard CMOS technology. The chip features a PD with a 10µm×10µm light-receiving area, employing techniques such as lateral interdigitated structure and shallow trench isolation to overcome the inherent bandwidth and responsivity limitations of CMOS PDs. Concurrently, the TIA circuit employs a fully inverter-based design with carefully inserted interstage inductors, significantly reducing power consumption and in-band noise. This research provides a practically valuable technical solution for designing low-cost, low-power high-speed optical receivers, achieving the highest reported speed for a fully integrated CMOS optical receiver to date.

Figure 5: System architecture and chip performance demonstration of the high-speed optical receiver chip

Dongshen Zhan (a 2023 master's student and 2023 SUSTech undergraduate graduate) is the first author of the paper. Professor Quan Pan is the sole corresponding author, and the School of Microelectronics at SUSTech is the sole affiliated institution. This work was primarily supported by the Shenzhen Science and Technology Major Program.

Related Papers from the Team

X. Cheng, H. Wu, Z. Li, W. Wu, X. Luo, Y. Zhang, Q. Pan, "8.9 A 72Gb/s/pin Single-Ended Simultaneous Bi-Directional Transceiver with C-Peaking Leakage Cancellation and Dual-Loop Hybrid Impedance Calibration for Chiplet Interfaces," *2026 IEEE International Solid-State Circuits Conference (ISSCC)*, San Francisco, CA, USA, 2026, pp. 150-152, doi: 10.1109/ISSCC49663.2026.11409339.

Link: https://ieeexplore.ieee.org/abstract/document/11409339

H. Wu, X. Cheng, Y. Zhang, X. Luo, Z. Li, W. Wu, Q. Pan, "A 72Gb/s/pin Single-Ended Driver-Cooperative Coded PAM3 Transceiver with Asymmetric Data-Dependent Equalization and Bias-Peaking for Chiplets and Memory Interfaces," *2026 IEEE International Solid-State Circuits Conference (ISSCC)*, San Francisco, CA, USA, 2026, pp. 624-626, doi: 10.1109/ISSCC49663.2026.11409257.

Link: https://ieeexplore.ieee.org/abstract/document/11409257

D. Zhan, H. Wang, X. Luo, Y. Zhang, Z. Yao, W. Zhou, Z. Li, H. Wu, D. Zhou, and Q. Pan, "A Monolithic CMOS 28Gb/s PAM-4 Optical Receiver Front-End with Lateral-Enhanced P-Well/N-Well APD for VCSEL-Based Links," in Optical Fiber Communication Conference (OFC), Los Angeles, USA, 2026.

Link: https://www.ofcconference.org/schedule/#/Thursday

Z. Li, W. Zhou, W. Xiao, X. Luo and Q. Pan, "A 50 Gb/s PAM-4 Receiver Featuring Current-Reuse AFE and Single-Loop Half-Rate Reference-Less Bang-Bang CDR in 40-nm CMOS," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 73, no. 3, pp. 1900-1912, March 2026, doi: 10.1109/TCSI.2025.3620088.

Link: https://ieeexplore.ieee.org/abstract/document/11214700

Y. Zhang, L. Zhong, T. Fan, X. Luo, H. Wu, X. Cheng, W. Wu, W. Zhou, D. Xu, Q. Pan, "A 2 × 80 Gb/s Single-Ended TAS-TIS PAM-4 Receiver Front-End With Crosstalk Cancellation and Signal Reutilization in 28-nm CMOS," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 73, no. 1, pp. 126-139, Jan. 2026, doi: 10.1109/TCSI.2025.3591536.

Link: https://ieeexplore.ieee.org/abstract/document/11099549