current location :home>News

ISSCC (International Solid-State Circuits Conference), renowned as the "Olympics of Chip Design," is the most influential premier academic conference in the global integrated circuit field. The annual acceptance results represent the highest level of cutting-edge semiconductor research worldwide. ISSCC 2026 will be held in San Francisco, USA, in February 2026, drawing significant attention from both global academia and industry.

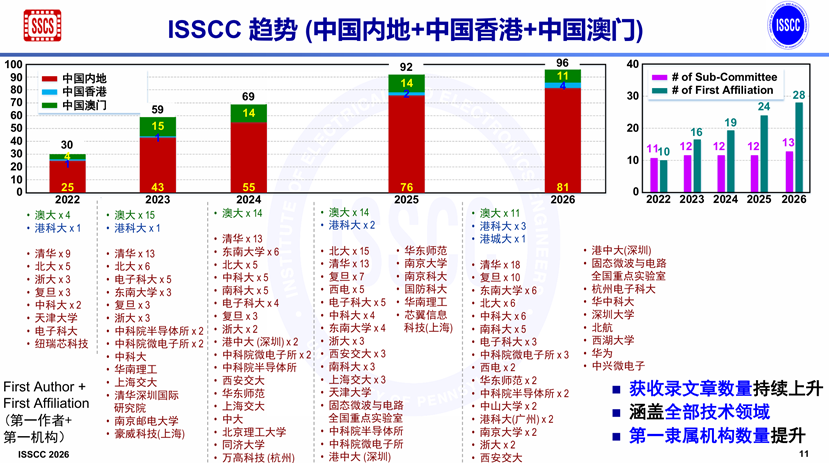

This year, ISSCC received a total of 1,025 submissions from top universities and industry institutions worldwide. Only 257 papers were ultimately accepted, with an acceptance rate below 25%. Each accepted paper represents the latest breakthrough in international chip technology.

This year, Southern University of Science and Technology (SUSTech) has successfully had five papers accepted at ISSCC, ranking the university among the global top 10 in terms of paper count. All five papers come from the School of Microelectronics, covering five different research directions. Among them, Associate Professor Jiamin Li's team contributed one paper, Assistant Professor Longyang Lin's team contributed two papers, and Professor Quan Pan's team contributed two papers.

This achievement not only demonstrates the School's sustained influence in the field of international chip research but also signifies breakthrough progress in key chip areas such as intelligent sensing, high-speed interconnects, extreme environment circuits, biomedical applications, and memory interfaces. The concentrated acceptance of five papers marks another important milestone in the accelerated advancement of the School's research capabilities.

ISSCC 2026 Global Top 10 Institutions by Number of Accepted Papers

The five accepted papers are:

(1) SESSION 7: Image Sensors and Ranging

*[7.8] A 55nm Intelligent Vision SoC Achieving 346TOPS/W System Efficiency via Fully Analog Sensing-to-Inference Pipeline*

Assistant Professor Longyang Lin's Team

First Author: Zhengke Yang (Master's student, Class of 2023)

(2) SESSION 8: Die-to-Die and High-Speed Electrical Transceivers

*[8.9] A 72Gb/s/pin Single-Ended Simultaneous Bi-Directional Transceiver with C-Peaking Leakage Cancellation and Dual-Loop Hybrid Impedance Calibration for Chiplet Interfaces*

Professor Quan Pan's Team

First Author: Xuxu Cheng (Ph.D. student, Class of 2021)

(3) SESSION 22: Circuits in Extreme Environments

*[22.4] A Radiation-Hardened Self-Healing CMOS Imager with Online Pixel/Logic Annealing and Tile-Adaptive Compression for Space Applications*

Assistant Professor Longyang Lin's Team

First Authors: Quan Cheng (Visiting Scholar), Zhengke Yang (Master's student, Class of 2023)

(4) SESSION 36: Neural and Biomedical Interfaces

*[36.3] A 16.4nJ/Class Patient-Independent Prototype-Based Spatio-Temporal CNN Processor with Forward-Inference-Based Adaptation for Robust and Low-Latency Seizure Detection*

Associate Professor Jiamin Li's Team

First Author: Yang Wang (Ph.D. student, Class of 2024)

(5) SESSION 37: Memory Interface

*[37.1] A 72Gb/s/pin Single-Ended Driver-Cooperative Coded PAM3 Transceiver with Asymmetric Data-Dependent Equalization and Bias-Peaking for Chiplets and Memory Interfaces*

Professor Quan Pan's Team

First Author: Hongzhi Wu (Postdoctoral Fellow)

Outstanding Performance: Highlighted Papers

The Program Committee selected 70 Highlighted Papers from the 257 accepted papers, contributed by 45 institutions from 9 countries. These include 46 papers from 28 universities, 22 papers from 15 companies, and 2 papers from 2 research institutions. China contributed a total of 24 Highlighted Papers (including 16 from Mainland China).

SUSTech has two papers selected as Highlighted Papers, ranking the university among the global top 10 institutions for Highlighted Paper count.

Brief Introduction of the Highlighted Papers:

[37.1] A 72Gb/s/pin Single-Ended Driver-Cooperative Coded PAM3 Transceiver with Asymmetric Data-Dependent Equalization and Bias-Peaking for Chiplets and Memory Interfaces

Authors: Hongzhi Wu, Xuxu Cheng, Yangyi Zhang, Xiongshi Luo, Zhenghao Li, Weitao Wu, Quan Pan

Professor Quan Pan's team at SUSTech proposed a 72Gb/s/pin PAM3 transceiver featuring TIA termination, including driver-cooperative coding, asymmetric data-dependent equalization, and bias-peaking. The TIA termination employing the driver-cooperative coding scheme significantly reduces static power, while the bias-peaking scheme reduces switching jitter and achieves better return loss.

[36.3] A 16.4nJ/Class Patient-Independent Prototype-Based Spatio-Temporal CNN Processor with Forward-Inference-Based Adaptation for Robust and Low-Latency Seizure Detection

Authors: Yang Wang, Longyang Lin, Jerald Yoo, Jiamin Li

Associate Professor Jiamin Li's team at SUSTech proposed a patient-independent seizure detection processor. It achieves 94.3%/94.9% sensitivity/specificity without requiring patient-specific data retraining. By calibrating with just two minutes of the patient's non-seizure EEG data, the adaptive detection performance is enhanced to 95.4%/97.9%. The prototype-based spatio-temporal CNN accelerator employs boundary feature reuse and risk-aware adaptive inference, reducing detection latency and energy consumption.