当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院刘小龙课题组在高性能锁相环和低噪声振荡器芯片设计领域取得重要进展,相关研究成果被国际顶级会议IEEE CICC2025和ESSERC2025录用。

论文1:高性能锁相环芯片

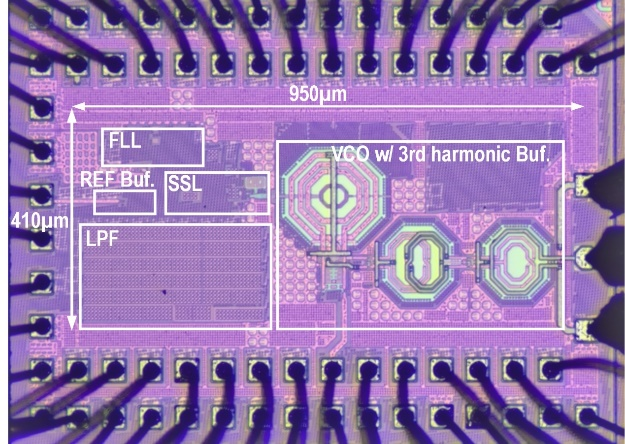

相关研究成果“A 24.6-to-30.6GHz Magnetic-Isolated Sub-Sampling PLL with a Fast-Locking FLL Achieving 64.9fs Jitter, -253.3dB FoMJ, and -69.1dBc Reference Spur in 65nm CMOS” 于2025年4月13-16日在美国波士顿举行的定制集成电路会议(IEEE Custom Integrated Circuits Conference, CICC 2025)上报告。该论文的第一作者为刘小龙课题组访问博士生曹瀚璋,通讯作者为刘小龙助理教授,第一单位为南方科技大学。

随着第五代移动通信技术的蓬勃发展,其赋能的万物互联及毫米波无线通信等应用对高频信号生成技术提出了严苛要求。亚采样锁相环通过直接采样振荡器信号,无需额外的分频器,避免了带内相位噪声恶化的问题,使其成为毫米波频段的理想选择。然而,亚采样锁相环的参考杂散抑制能力较弱。此外,其鉴相范围受限,需要依赖频率锁定环路的辅助,导致锁定时间较长。对于亚采样锁相环的设计,亟待在杂散性能与锁定时间上取得突破。

面对毫米波无线通信与高速有线通信的双重需求,本研究提出了一种基于磁隔离的亚采样锁相环架构。所设计的磁隔离亚采样鉴相器通过变压器实现了差模与共模信号的电磁隔离,消除了采样电容对振荡器差模谐振腔的周期性容性负载,从而抑制了二元频移键控效应导致的高参考杂散。同时,变压器提供的额外电荷到地的路径有效降低了采样过程中电荷共享与电荷注入效应的影响,进一步提升了参考杂散抑制能力。在锁定性能优化方面,本研究提出的快速锁定控制器实现了较小的Dead Zone范围,保证频率捕获范围的同时,将锁定时间缩短,并显著提升了锁定鲁棒性。

图1. 高性能锁相环芯片图

论文2:低噪声振荡器芯片

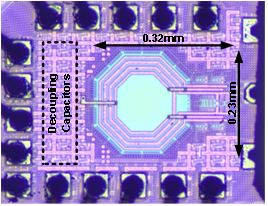

相关研究成果“A 7.7-to-10.1GHz Transformer-Based VCO Achieving 194.7dBc/Hz FoM and 206dBc/Hz FoMA with Third-Harmonic Impedance Expansion and Dual Common-Mode Resonances in 65nm CMOS” 被欧洲固态电子研究会议(European Solid-State Electronics Research Conference, ESSERC 2025)接收。该论文的第一作者为刘小龙课题组2022级博士生杨楷钿,通讯作者为刘小龙助理教授,第一单位为南方科技大学。

高性能振荡器在无线通信、雷达系统以及量子计算等领域发挥着重要作用。本论文基于三圈耦合变压器,提出了一款低功耗低噪声谐波整形振荡器。在不占用额外面积的情况下,所提出的谐振腔在差模激励下可以实现三次谐波阻抗扩展,在共模激励下可以实现二次和四次谐波阻抗,从而有效抑制有源器件的热噪声和闪烁噪声。同时,电源VDD和VSS的注入噪声也被有效抵消。该振荡器实现了优异的性能,功耗为1.2mW,综合FoM和FoMA分别为194.7和206dBc/Hz。

上述两项研究工作得到了国家自然科学基金和广东省自然科学基金项目的支持。

关于CICC

IEEE定制集成电路会议(CICC)是集成电路设计领域世界顶级会议之一,由IEEE固态电路协会(Solid-State Circuits Society)主办。CICC以论文录用率低、研究成果创新性和实用性强著称,每年吸引全球范围内大量学术界、工业界研发人员的关注和参与。

关于ESSERC

IEEE欧洲固态电子研究会议(ESSERC)是集成电路设计领域世界顶级会议之一,始创于1971年,由IEEE固态电路协会主办。ESSERC从2024年起由欧洲固态电路会议(ESSCIRC)和欧洲固态器件研究会议(ESSDERC)合并而成。ESSERC为固态器件和电路的最新进展提供一个年度欧洲论坛,促进技术专家、器件专家、集成电路设计师和系统设计师之间的交流互动。