当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院潘权副教授课题组在高速高密有线通信集成电路领域取得重要进展,针对正在激烈讨论的IEEE P802.3df标准进行开创性研究,提出两种可行性探索方案,为下一代有线通信接口标准提供了潜在的方法。两篇论文成果以“A 112-Gb/s Single-Ended PAM-4 Transceiver Front-End for Reach Extension in Long-Reach Link”[1]和“A 2×50 Gb/s Single-Ended MIMO PAM-4 Crosstalk Cancellation and Signal Reutilization Receiver in 28 nm CMOS”[2]为题发表在集成电路设计领域顶级会议IEEE European Solid-Sate Circuits Conference (ESSCIRC) 2022上。ESSCIRC为芯片设计领域四大顶级会议之一,代表电路设计领域最高水平,备受国内外产业界和学术界的高度关注。本年度ESSCIRC 有线收发机分会场面向全球工业界和学术界只接收4篇论文;其中,工业界分别接收了来自韩国Samsung Electronics和日本Kioxia Corporation的两篇文章,学术界接收的两篇论文全部来自南科大潘权团队。

另外,潘权团队在高速光通信集成电路设计领域也取得多项很有意义的进展”,研究成果以“112Gb/s PAM-4高速率可调多频段线性均衡器电路设计”[3]为题发表于IEEE International Conference on Integrated Circuits Technology and Applications (ICTA);以“160Gb/s PAM-4高速大输出摆幅的光调制驱动电路设计”[4]和“160Gb/s PAM-4高速低功耗的光接收器电路设计”[5]为题发表于IEEE Asia Pacific Conference on Circuits and Systems (APCCAS)。

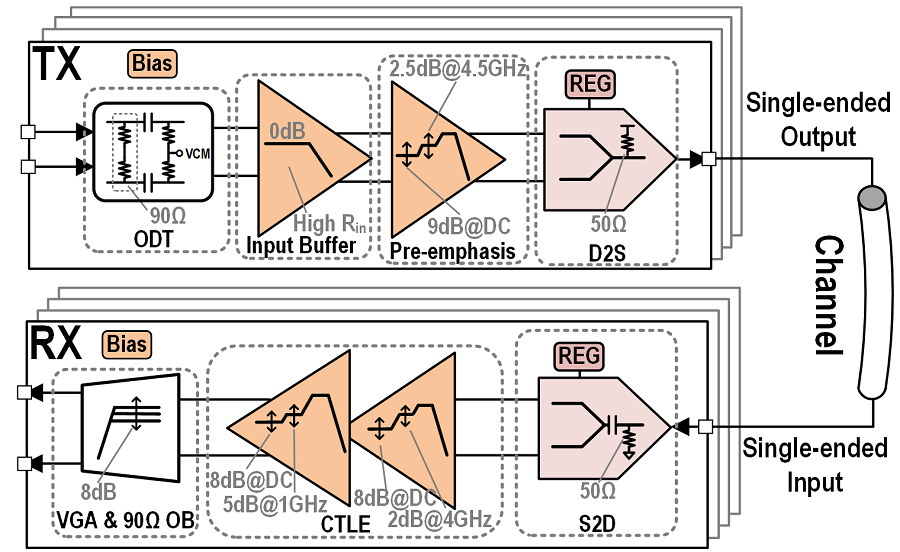

用于长距离通信链路延展的112Gb/s单端PAM-4收发器前端

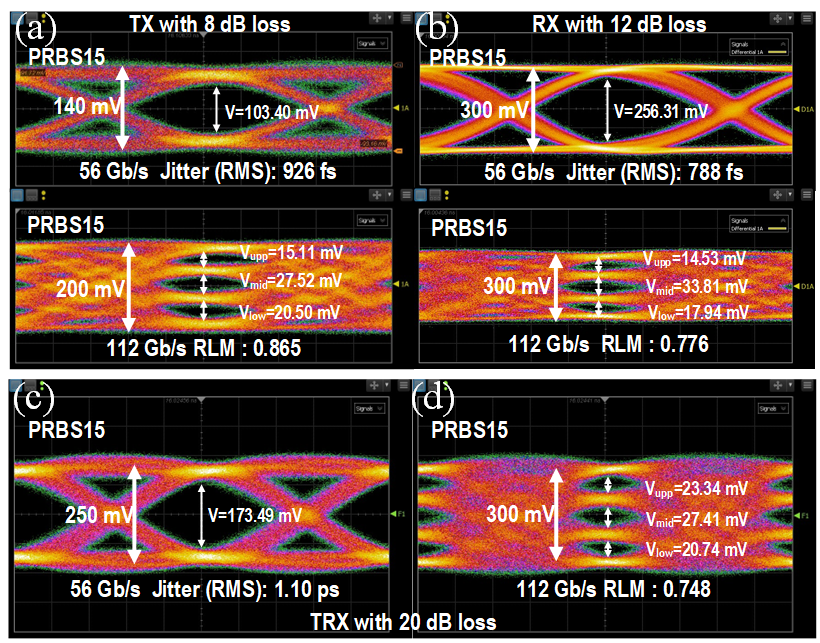

随着全球互联网流量的急剧增长,有线收发器(TRXs)需要更高的每车道数据速率。最近,IEEE P802.3 Beyond 400G以太网研究小组已经讨论了每车道200 Gb/s的信令方案。受无源链路的限制,特别是连接器和封装的带宽(BW)限制,传统的基于ADC-DSP的PAM-4方案可能无法支持长距离链路每车道224 Gb/s。目前,有三种可能的方案: 1)更先进的PAM方案,需要更好的线性度和信噪比;2)单端(SE)MIMO方案,需要差分对线之间的串扰消除;3) XSR/VSR SerDes +距离扩展TRX模块。在最后一种情况下,TRX模块用于差分到单端和单端到差分的转换,其中单端信号在由同轴电缆和连接器组成的单端无源信道中传输。单端信令可以显著提高I/Os的密度,从而有效地降低芯片封装和通信设备面板的复杂性。然而,实现单端112-Gb/s PAM-4信令传输的距离扩展模块的设计是很困难。在已有的单端电路报道中,记录的最高数据率为40 Gb/s。本文提出了一种基于130nm SiGe BiCMOS的支持PAM-4数据的小面积和低功耗的单端 TRX 前端,传输数据速率可达112 Gb/s。将TX前端的负电容器和RX前端的电感复用、非对称电感、群延迟失配校准相结合,实现20 dB的高均衡能力,1.81pJ/bit的能量效率,以及高性能的D2S-S2D转换,适用于400G以上的长距离扩展模块。

图1:论文[1]中单端PAM-4收发器前端的架构框图

图2:论文[1] 中单端PAM-4收发器前端的测试眼图

深港微电子学院22级博士生罗雄师和19级硕士生游薛伟为本论文的共同第一作者,潘权副教授为该论文唯一通讯作者,南方科技大学为该论文唯一通讯单位。

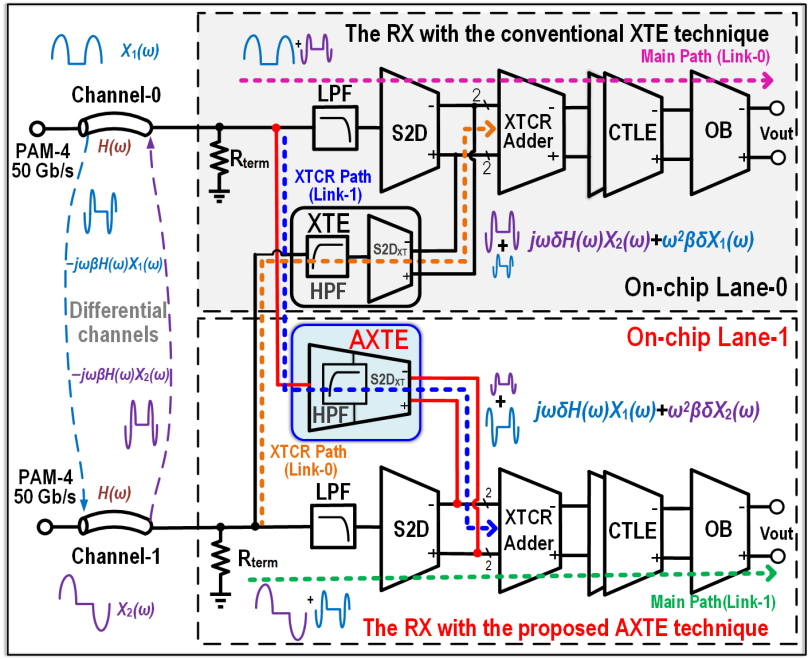

基于28nm CMOS的 2×50Gb/s 单端 MIMO PAM-4 串扰消除和信号再利用接收器

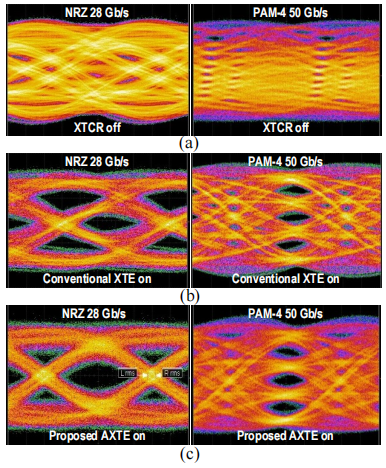

随着对高数据速率的需求激增,有线通信收发器(TRX)正面临新的挑战。由于来自电路、连接器、封装等方面的限制,每对差分电路要达到200Gb/s是极其困难的。因此,研究者值得探索突破这些限制的方法。目前,主流链路具有差分的输入输出,需要终端P和N,以及它们对应的返回参考来传输单向信号。值得注意的是,这些现有的无源差分链路可以被用作单端(SE)多输入多输出(MIMO)传输,以提高接口的通信效率和数据吞吐量。

本文提出了一种SE MIMO PAM-4 串扰消除和信号再利用(XTCR)接收器(RX),实现了2×50Gb/s的数据传输。其中,创新地提出了有源串扰提取(AXTE)和非对称电感峰值技术对电路进行优化,使其适用于400G电气接口的信号要求。此外,这项工作也提供了一种可能的方法,可在更先进的CMOS工艺中实现每对差分链路200 Gb/s的信号传输。

图3:论文[2]中SE MIMO接收器的架构框图

图4:论文[2]中SE MIMO接收器的测试眼图

深港微电子学院20级博士生钟立平为本论文第一作者,潘权副教授为该论文唯一通讯作者,南方科技大学为该论文唯一通讯单位。

高速率可调多频段线性均衡器电路设计

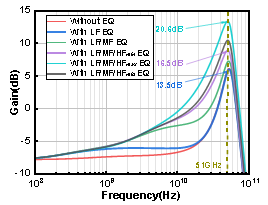

在高速芯片技术飞速发展的当今,为了满足高速数据互连的需要,对未来数据中心的扩展带宽和吞吐量提出了更高的要求。由于趋肤效应的影响,信号通道在高速传输过程中会引入相当大的高频损耗,这就对于均衡电路提出了更高的要求。传统的连续时间线性均衡器(CTLE)在SiGe BiCMOS工艺下主要侧重于高频的通道补偿,但忽略了中低频部分。潘权课题组发表的以 “A 200-Gb/s PAM-4 Feedforward Linear Equalizer with Multiple-Peaking and Fixed Maximum Peaking Frequencies in 130nm SiGe BiCMOS”[3]为题的论文提出了一种峰值可调的PAM-4线性均衡器,在130纳米SiGe BiCMOS工艺下用于200-Gb/s速率的通信。通过采用前馈和源退化技术,能够在高、中、低频下实现多频段均衡。此外,该均衡器可以通过数字信号控制实现在固定峰值频率51GHz下不同的补偿大小,保证电路在工艺、电压和温度的变化下足够的补偿精度。仿真结果表明,该电路在2.8/3.3V的电压下功耗为159mW,同时达到了0.80 pJ/bit的能效比。

图5:线性均衡器的仿真频率响应

深港微电子学院2019级本科生贾正哲为本论文第一作者,潘权副教授为通讯作者。本工作得到了广东省深圳市南山区科技创新局的项目支持。

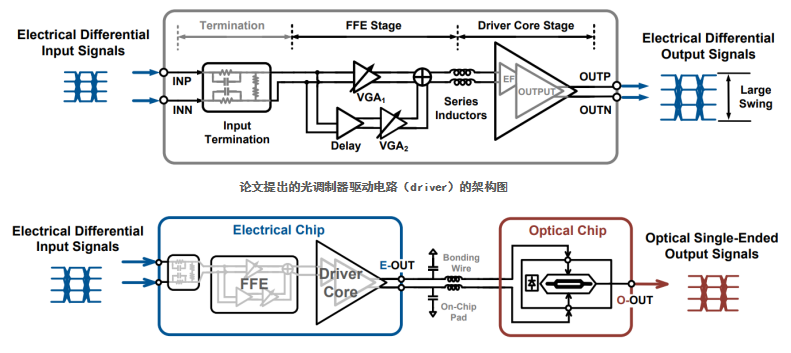

高速大输出摆幅的光调制驱动电路设计

随着物联网(IoT)、人工智能(AI)和云计算的快速发展,高性能的光通信系统在数据中心和城市网络中对于提高通信能力具有重要意义。具有高带宽和大输出电压摆动的驱动器,对于提高光信号的速度和消光比(ER)是必不可少的。由于光调制器存在随频率变化的损耗,在驱动器端采用均衡技术,可以减小信号的衰减。潘权课题组本科生冯硕、博士陈福栈等人采用130nm SiGe BiCMOS工艺,成功设计了一款高速、大输出摆幅的光调制驱动器(Optical Modulator Driver)。该成果以“A 4-Vppd 160-Gb/s PAM-4 Optical Modulator Driver with All-Pass Filter-Based Dynamic Bias and 2-Tap FFE in 130-nm BiCMOS”[4]为题发表。该论文提出的驱动器应用了基于全通滤波器(APF)的击穿电压倍增拓扑结构,以改善输出摆幅和带宽。一个2抽头的分数间隔(Fractional-Spaced)的前馈均衡器(FFE)被应用,以补偿光调制器的带宽。仿真结果表明,该驱动器可以实现4-Vppd的输出摆幅,62.4GHz的3-dB带宽,功耗为1.15W。为了进一步展示了该驱动器的性能,搭建了一个光电(Electrical/Optical)系统,其中使用了带宽为35GHz的MZM光调制器的Verilog-A模型。利用2抽头FFE的均衡,E/O系统实现了50.4GHz的3分贝带宽,可以支持160-Gb/s的PAM-4光通信,达到国际同类型电路最佳水平。

图6:论文[4]中搭建的光电连仿系统

深港微电子学院的2019级本科生冯硕和2020级博士生陈福栈为本论文共同第一作者,潘权副教授为唯一通讯作者,南科大为论文唯一单位。

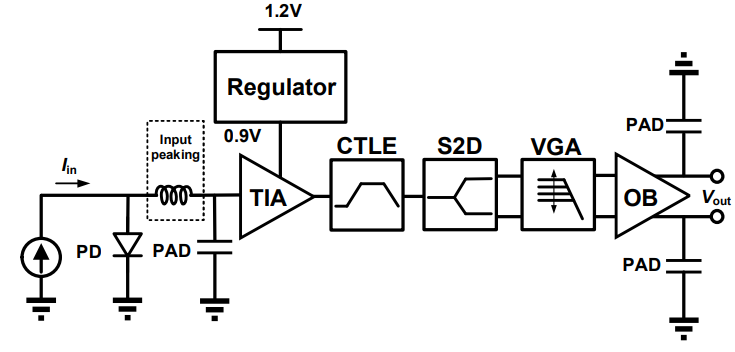

高速低功耗的光接收器电路设计

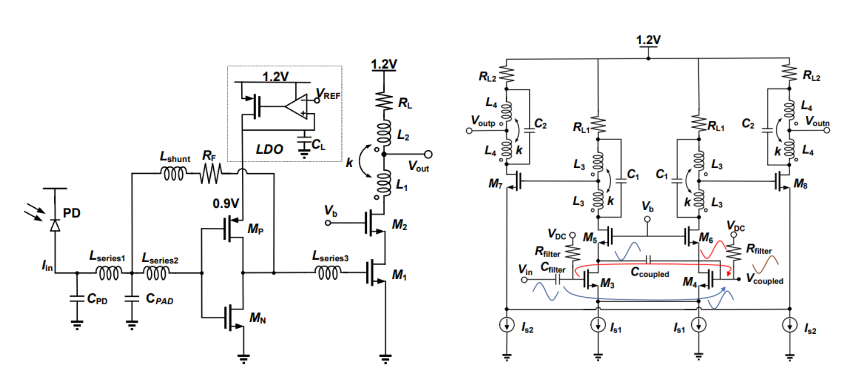

随着云计算设备和多媒体设备数目的飞速增长,流向数据中心的数据量迅速增加。因此,需要有更高带宽的接口芯片来支持超高速通信。相较于传统的铜互连电路,高速光通信电路凭借其稳定、高能效和极低的信道损耗等优点被广泛用于各大数据中心,跨阻放大器(Transimpedance Amplifier,TIA)是高速光通信电路的核心模块。潘权课题组本科生王磊明等人采用28nm CMOS工艺,成功设计了一款具有单端输入和差分输出的160Gb/s PAM4光接收器(Optical Receiver)。该成果以“A 160-Gb/s 0.37-pJ/bit PAM4 Optical Receiver in 28-nm CMOS”V[5]为题发表。该接收器包括一个基于反相器的均衡跨阻放大器(TIA)、一个级联的单差分转换器(S2D)和两级可变增益放大器(VGA)。在均衡的TIA和S2D中采用了电感峰值技术以扩大带宽。该论文所提出的接收器消耗58.79mW的功率,实现了76.12dBΩ的差分转换增益,增益和相位差分别为0.2dB和3.2°。

图7:论文[5]提出的光接收器电路(Optical Receiver)的架构图

图8:论文[5]提出的TIA和CTLE电路结构图(左图),论文[5]中提出的两级S2D电路结构图(右图)

深港微电子学院的2018级本科生王磊明为本论文学生第一作者,潘权副教授为通讯作者,南科大为论文唯一单位。

论文信息:

[1] X. Luo, X. You, J. Fu, Z. Li, L. Zhong, T. Fan, Z. Qiu, W. Xiao, Y. Chen, Q. Pan*, “A 112-Gb/s Single-Ended PAM-4 Transceiver Front-End for Reach Extension in Long-Reach Link,” in IEEE European Solid-Sate Circuits Conference (ESSCIRC), 2022.

[2] L. Zhong, H. Wu, W. Wu, W. Xiao, X. Luo, D. Xu, X. Cheng, Z. Li, T. Fan, Q. Pan*, “2×50 Gb/s Single-Ended MIMO PAM-4 Crosstalk Cancellation and Signal Reutilization Receiver in 28 nm CMOS,” in IEEE European Solid-Sate Circuits Conference (ESSCIRC), 2022.

[3] Z. Jia, T. Fan, D. Xu, D. Zhan, L. Hu, Z. Zhang, Y. Wang, C. Chen, X. Liu, H. Wu Q. Pan*, “A 200-Gb/s PAM-4 Feedforward Linear Equalizer with Multiple-Peaking and Fixed Maximum Peaking Frequencies in 130nm SiGe BiCMOS,” in IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), 2022.

[4] S. Feng, F. Chen, Z. Li, W. Zhou, D. Xu, C. Chen, X. Liu, H. Wu, Q. Pan*, "A 4-Vppd 160-Gb/s PAM-4 Optical Modulator Driver with All-Pass Filter-Based Dynamic Bias and 2-Tap FFE in 130-nm BiCMOS," in IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 2022.

[5] L. Wang, X. Luo, D. Xu, Z. Qiu, Y. Yan, Q. Pan*, "A 160-Gb/s 0.37-pJ/bit PAM4 Optical Receiver in 28-nm CMOS," in IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 2022.