当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院余浩教授课题组在高性能片上超材料等离子体I/O芯片(Silicon Surface Plasmonic I/O Interface)方向取得突出成果。余浩教授课题组采用 65nm CMOS工艺,成功设计和验证了一款140GHz 13.5Gb/s表面等离子体I/O通信收发系统。相关成果以“A 13.5-Gb/s 140-GHz Silicon Redriver Exploiting Metadevices for Short-Range OOK Communications”为题发表在毫米波电路设计领域顶级期刊IEEE Transactions on Microwave Theory and Techniques(TMTT)上。其主要解决电学I/O的信道串扰,功耗和延迟问题。

下一代千核服务器对全集成片上I/O的通信质量有着较高要求, 其包括1)高速,2)低串扰,3)低延迟,4) 低功耗, 5)全集成,6)低造价。光学I/O具有高速,低串扰,以及低功耗的优势,但全集成有较高难度且造价昂贵。电学数字基带I/O有全集成,低造价的优势,但其通信质量受限于信道间串扰,且延迟和功耗较大。

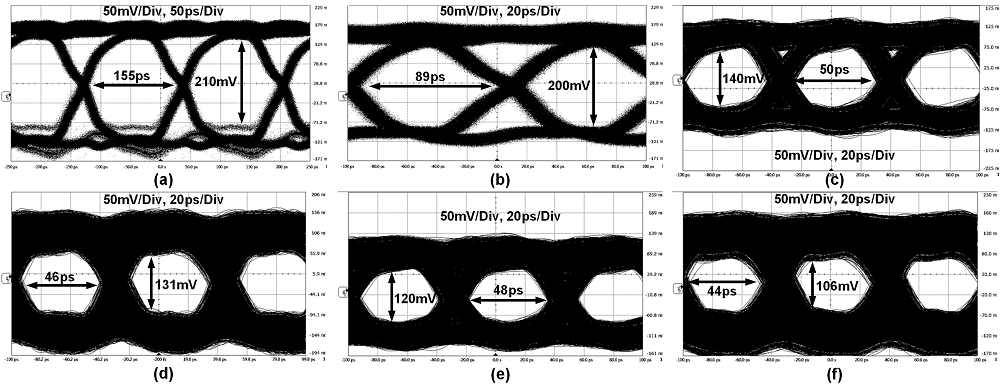

针对上述问题,该论文提出了1)可以高效降低信道电磁串扰的表面波传输线,2)基于Split-ring resonator (SRR) 的高消光比无源幅度调制器,3)基于表面波传输线和SRR的高效功率合成振荡器,和4)基于上述三种器件的低串扰低功耗I/O系统。其中,相邻两根信道的高频电磁串扰可以通过设计表面波传输线来有效降低。同时,使用基于SRR的幅度调制器实现了43dB的消光比, 并且不消耗直流功耗, 从而极大降低调制所产生的功耗。另外,所设计的表面波功率合成振荡器在140GHz产生5.3dBm的输出功率。由上述所提出的超材料器件搭建的I/O系统在仅仅2.4微米的信道距离上仍然可以传输13.5Gb/s/lane的数据,实现小于10-12的误码率和小于10ns的延迟。然而,采用传统传输线的140GHz I/O由于信道间的显著串扰而使得传输数据眼图完全关闭, 因而导致传输错误。所提出的电路在1.2V电压供电下实现的能效比为2.6 pJ/bit/lane,达到国际同类型I/O系统最佳水平。

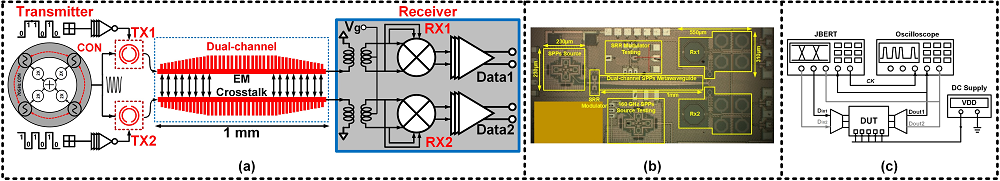

(a) 团队所提出的片上表面波I/O系统图, (b) 芯片显微镜,(c) 测试环境及仪器。

眼图测试结果: (a) 单信道27–1,6-Gb/s数据传输; (b) 单信道 27–1,9-Gb/s数据传输, 其中接收机由0.9V电压供电;(c) 单信道 27–1,13.5-Gb/s数据传输;(d) 双信道27–1,13.5-Gb/s数据传输;(e) 单信道 231–1,13.5-Gb/s数据传输;以及 (f) 双信道231–1,13.5-Gb/s数据传输。

I/O芯片广泛用于高速光通信,电通信和太赫兹通信系统中。本领域对研究能力有较高的要求,并且需要深厚的技术积累。该研究工作将促进千核服务器以及太赫兹领域有线通信的研究,实现高性能低串扰全集成I/O技术,并推动其产业化的进程。

本论文通讯作者为余浩教授,以南方科技大学为通讯单位。该研究工作同时得到未来通信集成电路教育部工程研究中心支持。

未来通信集成电路教育部工程研究中心于2019年10月获批成立。中心计划投入2000万元,以国家科学与技术发展规划为指导,精准对接我国“以创新驱动5G发展,突破关键核心技术”等的战略需求,针对适用于当前5G和未来通信应用集成电路关键共性技术(未来通信集成电路设计、宽禁带半导体材料与器件、先进制造与器件(传感器、存储器))的下一代通信系统展开研究,推进成果产业化,研究提出或积极参与行业技术标准与规范。同时,中心注重培养和集聚高层次的科技创新人才和管理人才,形成不断创新的可持续发展能力,为推动我国5G和未来通信的快速发展提供有力支撑。中心已经建立起高速高频通信电路测试平台(~1000万元投入)。中心已建成超百人的人才队伍,在有线/无线通信芯片、光通信芯片、氮化镓(GaN)功率器件、新型驻极体加工工艺等领域取得了多项突破性成果,并已形成20余项工程化案例。