current location :home>News

With the rapid development of artificial intelligence (AI) supercomputers, cloud computing, and core network switch, higher requirements for scalable bandwidth and throughput of future data centers have been put forward in order to meet high-speed data interconnection and switching requirements.

Professor Quan Pan’s team from the National Exemplary School of Microelectronics of the College of Engineering at the Southern University of Science and Technology (SUSTech) has recently made significant progress in the field of high-performance communication chip design, with research results including a 112-Gb/s Single-Ended PAM-4 Transceiver, a PAM-4 Crosstalk Cancellation and Signal Reutilization Receiver, a 4-Vppd 160-Gb/s PAM-4 Optical Modulator Driver and so on.

They conducted a pioneering study on the IEEE P802.3df standard and proposed two feasible exploration options, providing a potential approach for the next-generation wireline communication interface standard.

Their research results have been presented in at IEEE European Solid State Circuits Conference (ESSCIRC) 2022, a top conference in integrated circuit design, IEEE International Conference on Integrated Circuits Technology and Applications (ICTA), and IEEE Asia Pacific Conference on Circuits and Systems (APCCAS).

A 112-Gb/s single-ended PAM-4 transceiver front-end for reach extension in long-reach link

With the dramatic increase in global Internet traffic, wireline transceivers (TRXs) require higher data rates per lane. Recently, the IEEE P802.3 Beyond 400G Ethernet research group has discussed a 200 Gb/s signaling scheme per lane. Due to the limitations of passive links, especially the bandwidth limitations of connectors and packaging, traditional ADC-DSP-based PAM-4 solutions may not be able to support 224 Gb/s per lane for long-distance links.

Currently, there are three possible solutions. Firstly, a more advanced PAM solution that requires better linearity and signal-to-noise ratio; secondly, a single-ended MIMO solution that requires crosstalk cancellation between differential pairs; thirdly, XSR/VSR SerDes + Distance extension TRX module. In the last case, TRX modules are used for differential-to-single-ended and single-ended-to-differential conversions, where single-ended signals are transmitted in single-ended passive channels consisting of coaxial cables and connectors.

Single-ended signaling can significantly increase the density of I/Os, effectively reducing the complexity of chip packaging and communication equipment panels. However, it is very difficult to design a distance extension module for single-ended 112-Gb/s PAM-4 signaling transmission. The highest recorded data rate in existing single-ended circuit reports is 40 Gb/s.

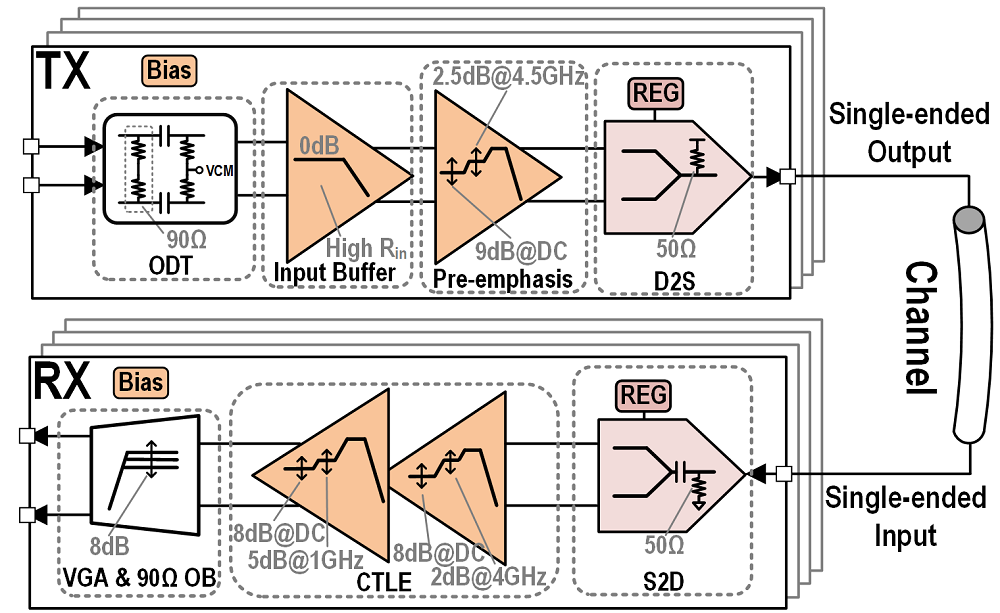

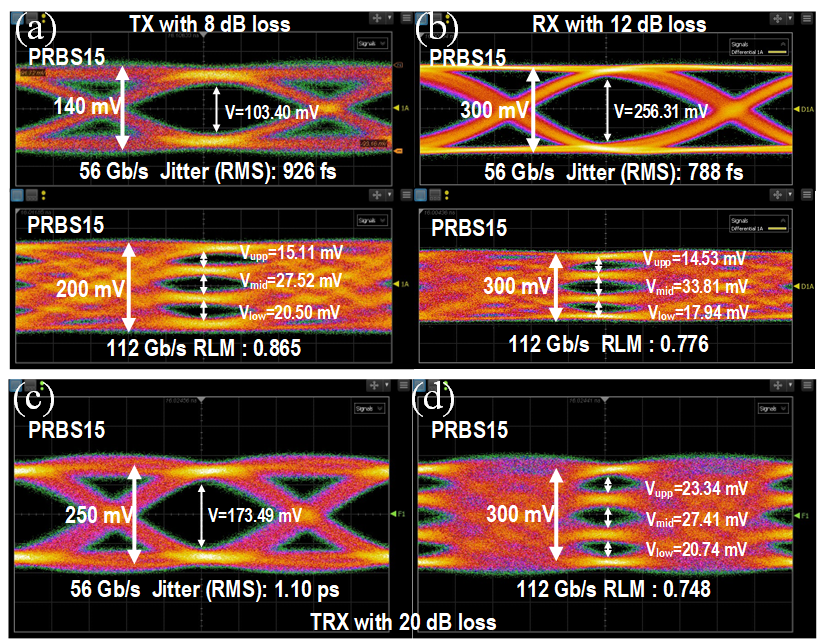

Prof. Pan’s team proposed a small-area and low-power single-ended TRX front-end supporting PAM-4 data based on 130nm SiGe BiCMOS, and the transmission data rate can reach 112 Gb/s. Combining the negative capacitor of the TX front end and the inductance multiplexing, asymmetrical inductance, and group delay mismatch calibration of the RX front end, it achieves a high equalization capability of 20 dB, energy efficiency of 1.81pJ/bit, and high-performance D2S-S2D conversion, suitable for long-distance expansion modules above 400G.

This work, entitled “A 112-Gb/s Single-Ended PAM-4 Transceiver Front-End for Reach Extension in Long-Reach Link,” has been accepted in ESSCIRC 2022.

Xiongshi Luo, a doctoral student, and Xuewei You, a master’s student, both of SME at SUSTech, are the co-first authors of this paper. Prof. Quan Pan is the only corresponding author of this paper, and SUSTech is the only corresponding unit.

Figure 1. Architecture block diagram of the single-ended PAM-4 transceiver front-end in paper

Figure 2. The test eye diagram of the single-ended PAM-4 transceiver front-end in the paper

A 2×50 Gb/s Single-Ended MIMO PAM-4 Crosstalk Cancellation and Signal Reutilization Receiver in 28 nm CMOS

With the recent surge in the demand for high data rates, wireline communication transceiver (TRX) faces new challenges. Considering the various limitations of circuits, connectors, packages, etc., it is extremely difficult to achieve 200 Gb/s per differential link. Therefore, it is worthwhile for researchers to explore interesting ideas that break through these limitations. Nowadays, mainstream links are with differential input-outputs, requiring both terminals P and N, and their corresponding return references to transmit one-way signals. However, these existing differential links can be easily used as single-ended (SE) multiple-input multiple-output (MIMO) transmission to improve I/O efficiency and data throughput.

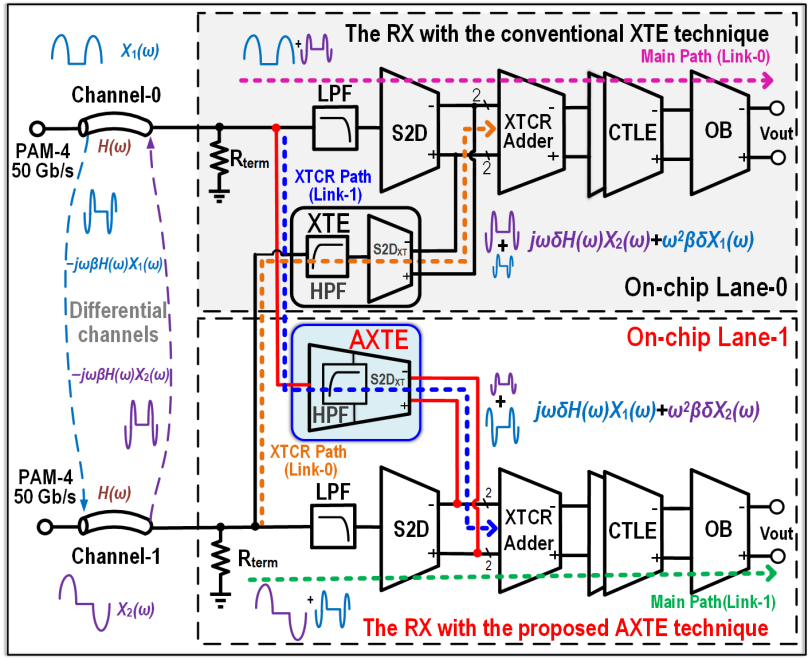

In this study, Prof. Pan’s team proposes a SE MIMO PAM-4 crosstalk cancellation and signal reutilization (XTCR) receiver (RX), realizing 2×50 Gb/s data transmission. The active crosstalk extraction (AXTE) and the asymmetric inductor peaking technique are proposed to optimize the circuit, making it suitable for supporting the signaling requirements of 400G Electrical Interfaces. Moreover, this work also provides a promising method to realize 200 Gb/s per differential or differential-like link in more advanced technologies.

This work, entitled “A 2×50 Gb/s Single-Ended MIMO PAM-4 Crosstalk Cancellation and Signal Reutilization Receiver in 28 nm CMOS”, has been accepted in ESSCIRC 2022.

Liping Zhong, a Ph.D. student of SME at SUSTech, is the first author of this paper. Prof. Quan Pan is the sole corresponding author, and SUSTech is the only corresponding unit.

Figure 3. Top architecture of the proposed SE MIMO XTCR link

Figure 4. Measured eye diagram of the SE MIMO receiver in paper

High-speed linear equalizer with multiple-peaking design

With the rapid development of high-speed chip technology today, higher demands are put forward in order to meet high-speed data interconnects and exchange requirements for extended bandwidth and throughput in future data centers. Due to the skin effect, signal channels introduce considerable high-frequency loss during high-speed transmissions, necessitating greater demands on equalization circuits. Conventional continuous-time linear equalizers (CTLEs) in the SiGe BiCMOS process mainly focus on channel compensation at high frequencies, but ignore the low and middle-frequency parts.

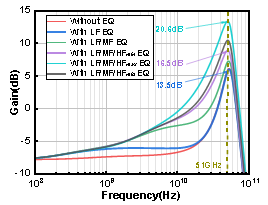

In this paper, Prof. Pan’s team proposes a peak-tunable PAM-4 linear equalizer for 200-Gb/s communication in a 130-nm SiGe BiCMOS process. The feedforward and degeneration techniques are employed to realize multiple peaks at high, middle, and low-frequency points, respectively. Moreover, the equalizer can be digitally controlled to achieve different compensation sizes at a fixed peak frequency of 51GHz, guaranteeing the circuit sufficient compensation accuracy under process, voltage, and temperature (PVT) variations. The simulation results show that it consumes 159-mW power under 2.8/3.3-V supply and achieves 0.80-pJ/bit power efficiency.

This work, entitled “A 200-Gb/s PAM-4 Feedforward Linear Equalizer with Multiple-Peaking and Fixed Maximum Peaking Frequencies in 130nm SiGe BiCMOS,” has been accepted in ICTA 2022.

Zhengzhe Jia, an undergraduate student of SME at SUSTech, is the first author of this paper. Prof. Quan Pan is the corresponding author.

Figure 5. Simulated frequency response of the linear equalizer

Design of high-speed, large-swing optical modulation driver

With the rapid development of the Internet of Things (IoT), artificial intelligence (AI), and cloud computing, high-performance optical communication systems are of significance in data centers and metro networks for improving communication capacities. In order to improve the speed and the extinction ratio (ER) of optical signals generated by optical modulators, a driver with high bandwidth and a large output voltage swing is essential. However, the signal degradation due to the frequency-dependent loss of optical modulators makes stringent demands on the equalization techniques at the driver side.

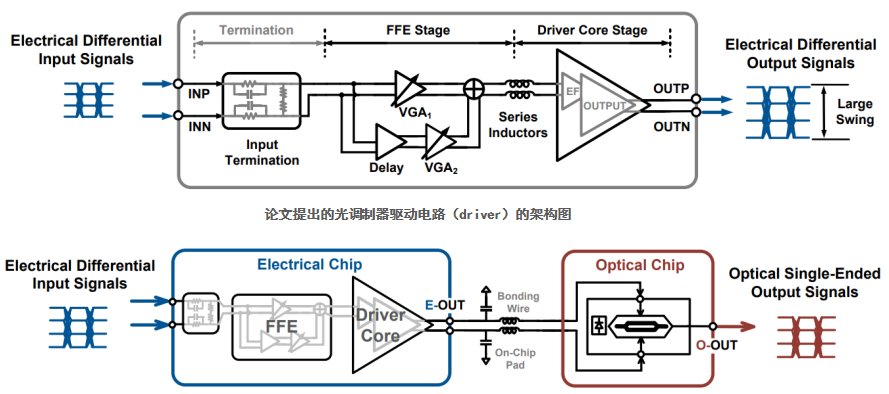

Prof. Pan’s group successfully designed a high-speed, large output swing optical modulator driver using a 130-nm SiGe BiCMOS process. Their work presents a high-speed, large output swing driver with a 2-tap feed-forward equalizer (FFE) for optical modulators in a 130-nm SiGe BiCMOS process. A breakdown voltage (BV) doubler topology with all-pass filter (APF)-based dynamic bias is applied in the driver to improve the output swing and the bandwidth. A 2-tap fractional-spaced FFE is implemented to compensate for the insufficient bandwidth of optical modulators.

Simulation results indicate that the driver achieves an output swing of 4 Vppd and a 3-dB bandwidth of 62.4 GHz with a power consumption of 1.15 W. The driver's performance is further evaluated in an electrical/optical (E/O) system where a Verilog-A model for Mach-Zehnder Modulator (MZM) with a 3-dB bandwidth of 35 GHz is used. Taking advantage of the 2-tap FFE, the E/O system achieves a 3-dB bandwidth of 50.4 GHz and can support 160-Gb/s PAM-4 optical communications.

This work, entitled “A 4-Vppd 160-Gb/s PAM-4 Optical Modulator Driver with All-Pass Filter-Based Dynamic Bias and 2-Tap FFE in 130-nm BiCMOS,” has been accepted in APCCAS 2022.

Shuo Feng, a 2019 undergraduate student, and Fuzhan Chen, a 2020 Ph.D. student, both of SME at SUSTech, are the co-first authors of this paper. Prof. Quan Pan is the sole corresponding author, and SUSTech is the only affiliated institution.

Figure 6. Electrical/optical (E/O) system with the proposed electrical driver and the optical MZM modulator

Circuit design of optical receiver with high speed and low power consumption

With the rapid increase in the number of cloud computing devices and multimedia devices, the amount of data flowing to the data center is increasing rapidly. Therefore, interface chips with higher bandwidth are required to support ultra-high-speed communication.

Compared with traditional copper interconnection circuits, high-speed optical communication circuits are widely used in major data centers due to their stability, high energy efficiency, and extremely low channel loss advantages. Transimpedance amplifiers are the core modules of high-speed optical communication circuits.

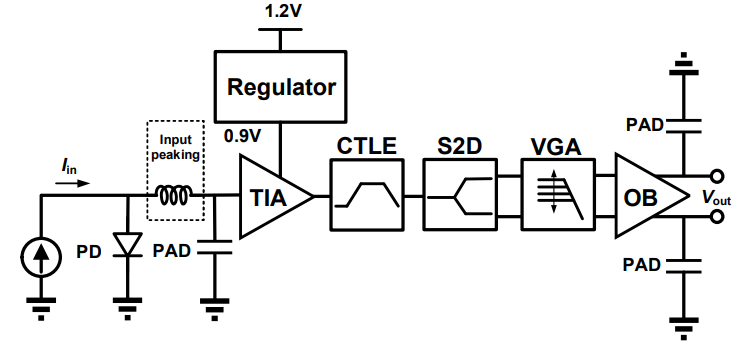

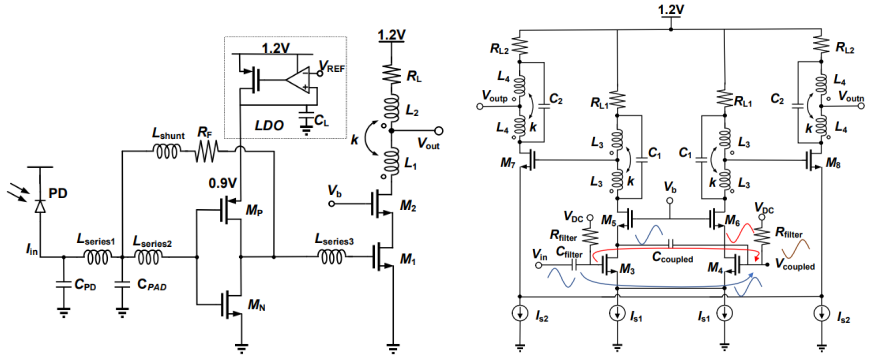

The researchers successfully designed a 160Gb/s PAM4 optical receiver with single-ended input and differential output using 28nm CMOS technology. The receiver consists of an inverter-based balanced transimpedance amplifier (TIA), a cascaded single-differential converter (S2D), and two stages of variable-gain amplifiers (VGA). Inductive peaking techniques are used in balanced TIA and S2D to expand bandwidth. The receiver proposed in this paper consumes 58.79mW of power and achieves a differential conversion gain of 76.12dBΩ with a gain and phase difference of 0.2dB and 3.2°, respectively.

This work, entitled “A 160-Gb/s 0.37-pJ/bit PAM4 Optical Receiver in 28-nm CMOS,” has been accepted in APCCAS 2022.

Leiming Wang, a 2018 undergraduate student from SME at SUSTech, is the first author of this paper. Prof. Quan Pan is the corresponding author, and SUSTech is the only corresponding unit.

Figure 7. Architecture diagram of the optical receiver circuit (Optical Receiver) proposed in the paper

Figure 8. TIA and CTLE circuit structure diagram proposed in the paper (left figure), two-stage S2D circuit structure diagram proposed in the paper (right figure)

These studies were supported by the Nanshan District Science and Technology Innovation Bureau. The authors also acknowledge the support of the State-Key Laboratory of Analog and Mixed-Signal VLSI and IME/ECE-FST, University of Macau.

ESSCIRC is one of the four top conferences in the field of chip design, representing the highest level in circuit design, and is of great interest to industry and academia at home and abroad.

Only four papers were accepted in this year’s ESSCIRC Wireline Transceiver Session for global industry and academia. Among them, two papers from the industrial sector, Samsung Electronics (Korea) and Kioxia Corporation (Japan), were accepted, and two papers from the academic sector, which were both from Prof. Quan Pan’s team at SUSTech.

Prof. Quan Pan’s research group welcomes outstanding undergraduates, graduate students, and postdoctoral fellows to join their team.

Paper links:

ESSCIRC 2022: https://ieeexplore.ieee.org/document/9911452

ESSCIRC 2022: https://ieeexplore.ieee.org/document/9911463

ICTA 2022: https://ieeexplore.ieee.org/document/9963128