当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院林龙扬课题组在非易失存算一体芯片领域取得重要研究进展。团队基于40纳米CMOS及STT-MRAM工艺,提出并流片验证了首个精度无损、全并行的数字式非易失存算一体芯片(nvDCIM, non-volatile Digital Compute-in-Memory),系统性解决了传统模拟式存算一体芯片在计算精度、可扩展性与鲁棒性上的瓶颈,并提出基于翻转率感知的网络训练方法以提升存算一体芯片在人工智能应用的能效。相关研究成果以“A lossless and fully parallel spintronic computeinmemory macro for artificial intelligence chips”为题发表于Nature Electronics(DOI:10.1038/s41928-025-01479-y)。研究由南方科技大学联合西安交通大学等单位共同完成,南方科技大学为论文第一单位和通讯单位。南方科技大学林龙扬助理教授、西安交通大学闵泰教授为论文的通讯作者。南方科技大学林龙扬课题组2024级博士研究生李瑚淼(南科大2018级本科毕业生,2022级硕士研究生)为论文的第一作者。

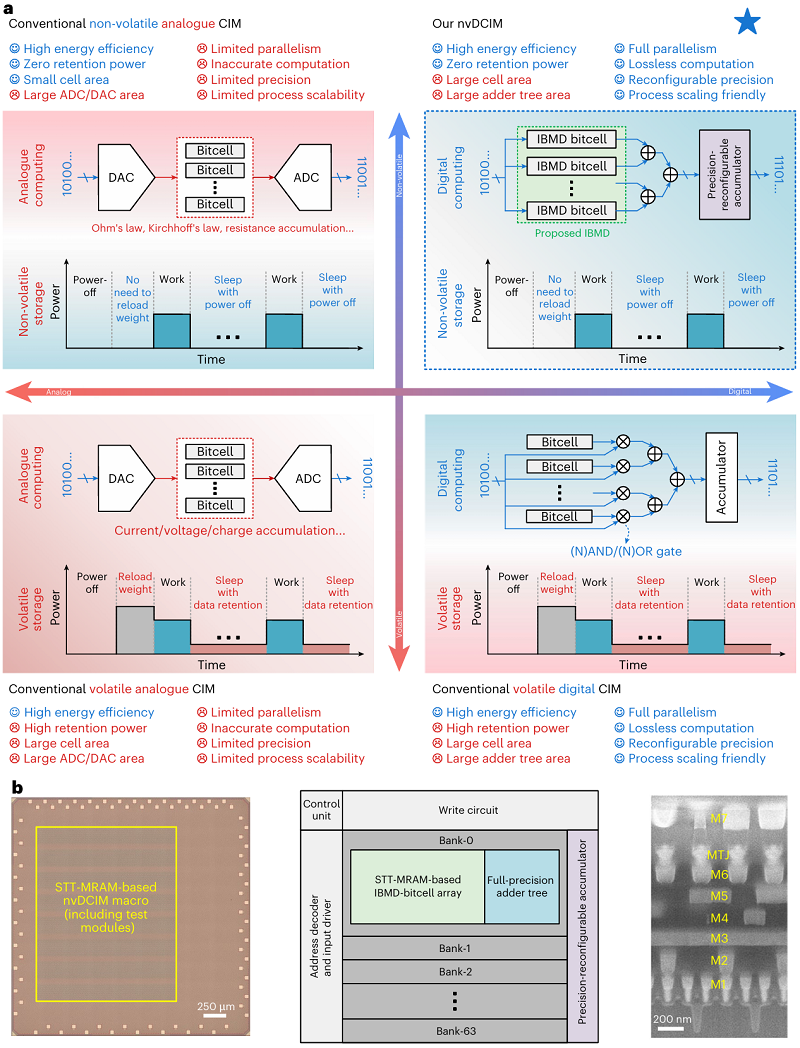

人工智能芯片的性能正日益受到传统冯·诺依曼架构中“存算分离”模式的制约,频繁的数据搬运导致高能耗与高延迟。非易失存算一体(nvCIM)架构将矩阵向量乘法(MVM)直接嵌入存储单元执行,从而显著降低数据移动的开销,为突破这一瓶颈提供了可行路径。然而,当前主流的模拟式nvCIM 架构存在计算精度受限、受工艺电压温度波动影响大、可扩展性差等问题。此外,在先进制程下,模拟电路中数模/模数转换器的设计也面临精度下降以及面积与功耗开销增大等挑战,限制了系统的可扩展性与鲁棒性。这些因素使得模拟式nvCIM 难以胜任物理信息神经网络(PINN)等对计算精度和可靠性要求严苛的人工智能驱动科学(AI for Science)研究任务。因此,如何在非易失存储上实现兼具高能效、高通量、全精度数字式计算,已成为该领域亟待突破的核心难题。

针对上述挑战,研究团队基于40纳米CMOS及STT-MRAM工艺,成功设计并流片验证了一款64 kb非易失数字式存算一体芯片,在存储单元、电路与算法三个层面实现了系统性创新:

1. 在存储单元层面,团队提出“单元内乘法与数字化” (IBMD,In-Bitcell Multiplication and Digitization),在STT-MRAM位单元中实现单比特输入与存储权重的乘法运算并直接输出数字化结果,等效实现数字“与”逻辑。该设计从源头避免使用模拟式nvCIM中常见的数模/模数转换器,有效提升了系统的鲁棒性与可扩展性。

2. 在电路层面,团队实现了全精度加法树与精度可重构累加器,支持4/8/12/16比特多种精度配置的输入与权重,实现了全并行、精度无损的MVM,在保证计算精度的同时大幅提升吞吐率。

3. 在算法层面,团队提出翻转率感知训练方法(Toggle-rate-aware Training),通过将存算一体阵列输入信号的比特翻转率作为正则项,融入神经网络损失函数中进行联合优化。该算法在不降低模型任务精度的前提下,显著降低了芯片在执行推理过程中的动态功耗,实现了软件与硬件协同优化能效的目标。

该研究展现了nvDCIM架构在实现高吞吐、高能效、无损数字式计算方面的综合潜力,为下一代高能效AI芯片提供了一条可靠路径。IBMD单元设计不仅成功在STT-MRAM中实现了高速数字逻辑运算,该方案还可进一步推广至其他阻性非易失存储技术,拓宽了nvDCIM的技术路线与应用场景。未来,团队将继续优化电路设计与芯片架构,推动存算一体芯片向更大容量发展,并探索在复杂AI系统中的集成应用。通过软硬件协同优化策略,该技术有望为打破“内存墙”、推动边缘与云端智能设备的高效能部署奠定坚实基础。

本研究获国家重点研发计划、国家自然科学基金、深圳市高等院校稳定支持计划等项目资助。

图1:基于非易失存储的数字存算一体(nvDCIM)芯片动机与概述