当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院陈全课题组在高性能电路仿真和芯片功率建模方向取得突破性研究进展,相关成果被国际电子设计自动化领域顶级会议ICCAD2025(International Conference on Computer-Aided Design)录用。相关工作得到国自然面上项目以及深圳市基础研究重点项目支持。

国际计算机辅助设计会议(ICCAD)是EDA领域水平最高的国际会议之一,由IEEE和ACM联合主办,创办于1982年,是中国计算机学会(CCF)推荐的计算机体系结构与高性能计算方向顶级国际学术会议。作为该领域历史最悠久、影响力最大的会议之一,ICCAD每年吸引全球众多高校、研究机构与工业界的顶尖研究者投稿与参会,具有极高的学术声誉和行业认可度。会议2025年文章投稿量逾千篇,接收率仅为24.7%。ICCAD2025将于2025年10月在德国慕尼黑举行。

论文1:高性能非线性电路仿真

在电路仿真领域,课题组提出了一种高性能、适用于通用非线性电路的瞬态仿真框架,论文题为“EI-TR: A Versatile Exponential Integrator Framework for Transient Analysis of Generic Nonlinear Circuits” 由2023级硕士研究生周航为第一作者,通讯作者为陈全副教授,南方科技大学为唯一完成单位。

瞬态仿真作为电子设计自动化(EDA)工具中的核心技术,在先进工艺节点下,大规模电路仿真的计算开销已成为设计流程中的关键瓶颈。指数积分法因具备高精度和高性能的潜力,被认为是下一代主流仿真方法的有力候选。但其在数值稳定性和与非线性求解(如牛顿迭代)的集成方面仍存在技术障碍,限制了其在实际电路中的推广应用。

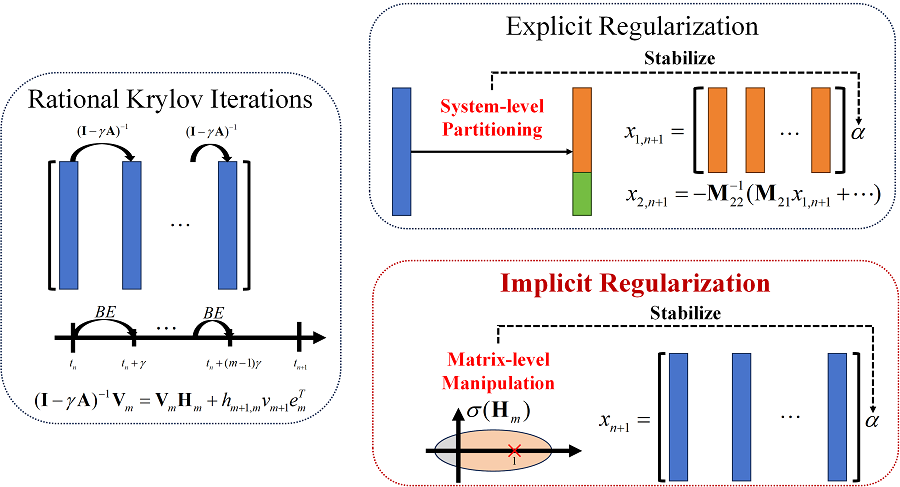

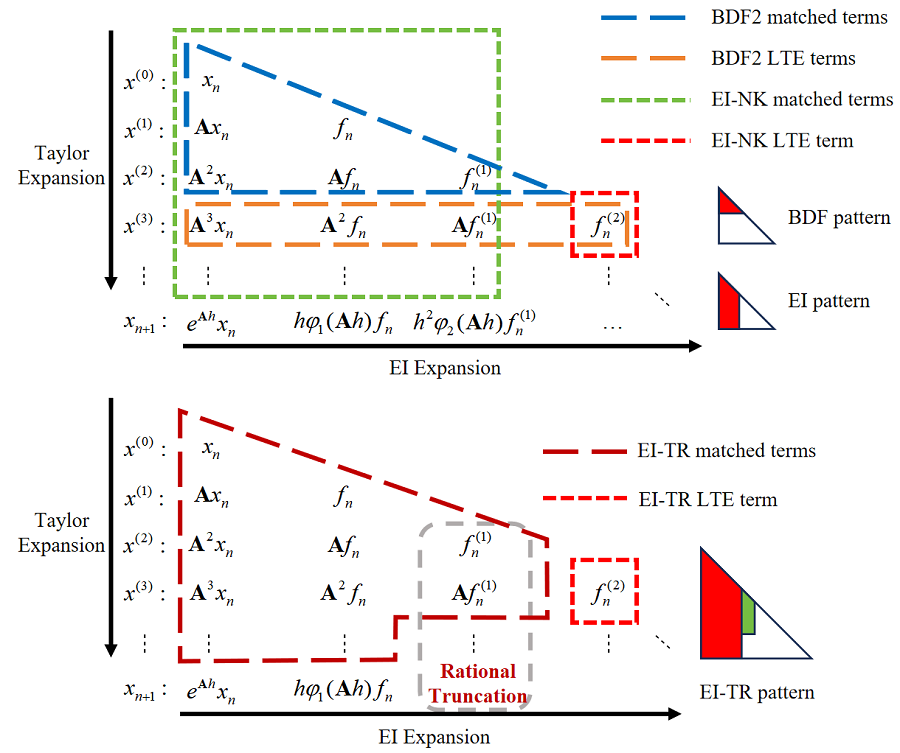

针对上述挑战,该工作提出了两项关键技术创新:隐式频谱规范化和有理函数截断方法。前者通过智能特征值调控机制,从源头上解决了指数积分法在非线性系统中的不稳定性问题,且几乎不增加额外开销;后者则通过引入合理的有理函数逼近策略,显著简化了指数算子与非线性项的复杂耦合,有效提升了整体计算效率。实验表明,在相同仿真精度的前提下,该方法性能相比传统SPICE工具提升最高可达23倍。

本研究为指数积分法在商用EDA工具中的落地提供了可行路径,为通用非线性电路的高效瞬态分析奠定了坚实基础,受到审稿人的高度评价。

图 1:隐式频谱规范化图示

图 2:有理函数截断原理图

论文2:芯片功率建模

“MF-MOR: Multi-Fidelity Model Order Reduction for Many-Port Linear Systems in Chip Power Modeling” 论文的第一作者为深港微电子学院2024级硕士研究生卢振杰,通讯作者为陈全副教授,南方科技大学为唯一完成单位。文章提出了一种面向芯片功率模型(CPM)的多保真度模型降阶方法(MF-MOR),为3DIC/Chiplet 架构下超大规模多端口系统(万级)的建模挑战提供了新的解决思路。

芯片功率模型(CPM)的抽取问题可归结为经典的RLC电路模型降阶任务。现有方法通常将芯片内部的大规模功率分布网(PDN)建模为RLC网络,并借助模型降阶技术压缩其复杂度,以支持芯片与封装协同仿真。但在3DIC等新兴架构中,面对期望单die级别的模型抽取,传统的投影式模型降阶方法难以应对成千上万个端口的系统,不仅性能低下,且存在精度不稳定的问题。此外,降阶模型的规模随端口数线性增长,也严重制约了其在现代IC设计流程中的应用。

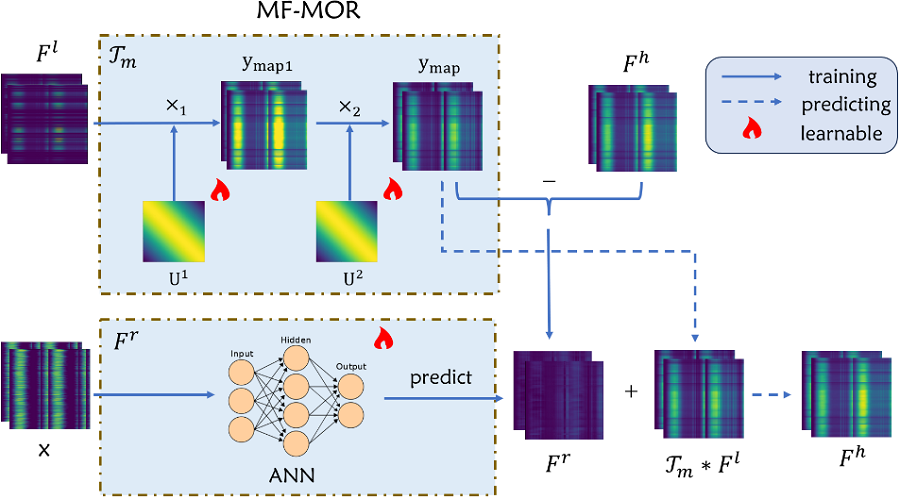

针对上述挑战,该工作提出了一种新型多保真度模型降阶方法MF-MOR。该方法首先通过端口压缩技术减少电路端口数量,然后对缩减后的电路模型进行初步降阶,得到一个粗略的低保真模型,并通过仿真获取低保真度输出。为修正因降阶与压缩带来的误差,进一步在原始系统上选取少量代表性输入进行高精度仿真,从而得到高保真输出。这两种数据共同用于训练一个补偿网络,该网络可以学习低保真度和高保真度响应之间的差异和相关性。在部署过程中,低保真模型和补偿网络成对使用,其中低保真模型进行仿真,其输出由补偿网络校正。数值结果表明,MF-MOR有效地处理了具有数百万个节点和数千个端口的PDN,与传统模型降阶方法相比,速度提高了27.74倍,降阶模型大小减小了47.78倍,精度相当或有所提高。还具有良好的输入的泛化能力。

图 3:MF-MOR多保真度补偿网络结构图