当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院2021级博士生李凯在多精度AI芯片设计领域取得新进展,其两篇文章分别被DATE和TVLSI接受。其中基于NAS多精度网络的高能效定点矢量脉动加速器芯片设计成果“A Precision-Scalable Energy-Efficient Bit-Split-and Combination Vector Systolic Accelerator for NAS-Optimized DNNs on Edge” 被欧洲设计自动化与测试会议(Design, Automation & Test in Europe Conference,DATE 2022)接收,同时,浮点高性能可重构AI计算“A Configurable Floating-Point Multiple-Precision Processing Element for HPC and AI Converged Computing”被IEEE超大规模集成电路系统期刊(IEEE Transactions on VLSI Systems, TVLSI)接收。

DATE会议与国际设计自动化会议(DAC)、国际计算机辅助设计会议(ICCAD)是EDA领域水平最高的三大国际主流会议,是中国计算机学会(CCF)推荐的计算机体系结构与高性能计算方向顶级国际学术会议,该会议每年文章投稿量近千篇,接收率仅有25%。TVLSI是集成电路领域的核心期刊,同样是中国计算机学会(CCF)推荐的计算机体系结构与高性能计算方向顶级期刊。

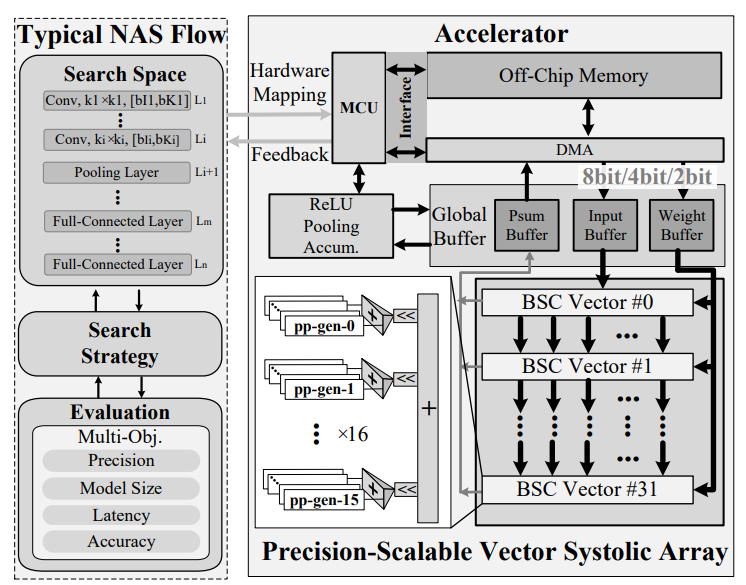

两篇文章均以南方科技大学为第一完成单位,其中基于NAS的多精度网络高能效多定点加速器芯片设计文章第一作者为2021级博士生李凯,该研究分析总结了提出的NAS多精度网络模型,4-bit精度的运算占据了总计算量的50%以上,因此,提出了基于bit-split-and-combination (BSC) 的新型多精度矢量运算单元,其以4-bit为基本运算单元,并结合提出的高效矢量脉动加速器,显著提高了基于NAS的多精度网络模型部署在边缘端的能量效率。功耗往往是制约神经网络模型部署在边缘端的关键,基于NAS的多精度网络模型在保证准确率的前提下压缩了网络模型大小,使得模型部署在边缘端成为可能,该工作基于NAS的多精度网络设计高能效多定点加速器芯片,对低功耗的边缘AI计算推理具有非常重要的意义。

图1:NAS多精度网络采用提出的BSC精度可伸缩的矢量脉动加速器结构

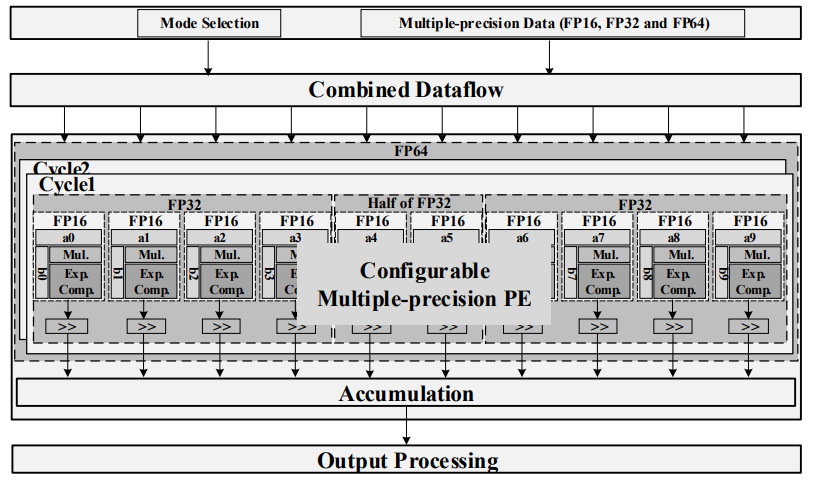

同时,2021级博士生李凯是浮点高性能可重构AI计算文章的学生第一作者,该研究提出了一种用于高性能可重构AI计算的多精度浮点运算处理单元,研究提出浮点可重构计算的最小冗余度设计,并基于高效SIMD架构大大降低硬件成本和指令交互过程,提高了运算速度和数据的处理能力。可以广泛应用在科学计算和机器学习训练中,解决处理器在进行多精度数据的处理过程中的瓶颈问题。

图2:高性能可重构的多精度浮点PE的整体结构

相关工作在深港微电子学院余浩教授课题组指导下完成,并受深圳市高层次人才团队项目和科技部国家重点研发计划项目“战略性科技创新合作”重点专项项目支持。