当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院潘权课题组在高性能通信芯片CDR(Clock and Data Recovery)方向取得突出成果。2019级硕士研究生肖文博、博士后黄奇伟、Hamed Mosalam等采用 40nm CMOS工艺,成功设计和验证了一款低功耗注入锁定型数据时钟恢复电路(ILCDR)。相关成果以“A 6.15―10.9 Gb/s 0.58pJ /bit Reference-Less Half-Rate Clock and Data Recovery with ‘Phase Reset’ Scheme”为题发表在集成电路领域顶级期刊IEEE Transactions on Circuits and Systems I: Regular Papers(TCAS-I)上。

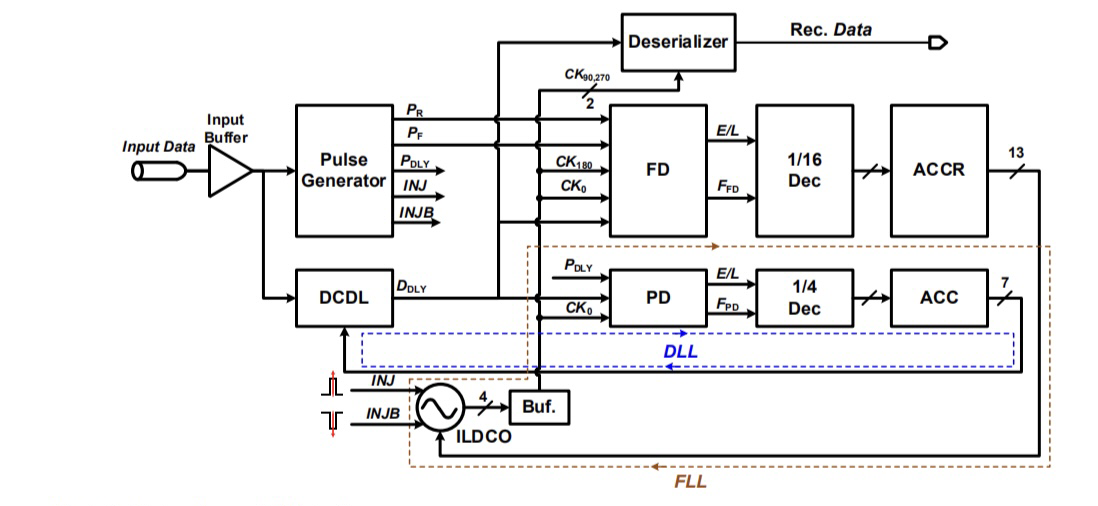

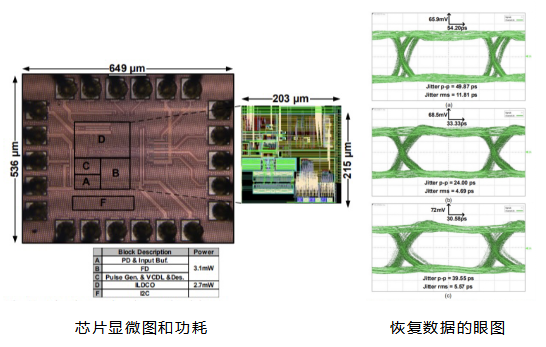

该论文提出了一种高效的“phase reset”方法以周期性对齐时钟和数据上升沿的相位。其中,频率误差则可通过BBPD比较数据上升沿和对齐后的时钟来提取。同时,使用低功耗两级注入锁定型环形数控振荡器提供了四相时钟并显著地减少了功耗。基于这种架构搭建的CDR在0.9V电源电压下功耗仅为5.8mW,经测量高频抖动容限(JTOL)为0.15UIpp。并且,提出的CDR在能量效率上实现了重大提升,能效比为0.58pJ/bit,能效比达到国际同类型电路最佳水平。

CDR芯片广泛用于高速光通信和电通信系统中。本领域对研究能力有较高的要求,并且需要深厚的技术积累。本论文设计始于2018年10月,2020年1月完成流片,2020年6月完成测试,2021年10月实现期刊发表,整个过程历时3年。

本论文共同第一作者为南科大微电子学院2019级硕士生肖文博、博士后黄奇伟(2020年成为华为海思高级芯片工程师),论文通讯作者是潘权教授,南科大是唯一通讯单位。

团队提出的新型超低功耗CDR系统架构图

参考文献:

W. Xiao#, Q. Huang#, H. Mosalam, C. Zhan, Z. Li and Q. Pan*, "A 6.15-10.9 Gb/s 0.58 pJ/Bit Reference-Less Half-Rate Clock and Data Recovery With ''Phase Reset'' Scheme," IEEE Transactions on Circuits and Systems I: Regular Papers, doi: 10.1109/TCSI.2021.3119907.