当前位置 :首页>新闻动态

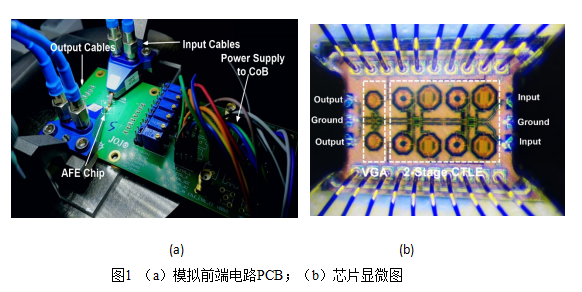

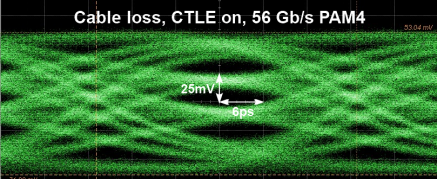

近日,南方科技大学深港微电子学院助理教授潘权课题组在AFE方向取得突出成果,课题组本科生李正浩、唐敏哲、樊泰扬采用TSMC 40nm CMOS工艺,设计了一款基于四电平脉冲幅度调制(4-Level Pulse Amplitude Modulation)传输方式的单通道56Gb/s高速SerDes模拟前端芯片。芯片测试成功后,在误码率、调节范围、稳定峰值、固定带宽方面有显著的优势。相关成果以“A 56-Gb/s PAM4 Receiver Analog Front-End with Fixed Peaking Frequency and Bandwidth in 40-nm CMOS”[1]为题发表在集成电路设计领域高水平期刊 IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II)上。

Analog Front-End(AFE),即模拟前端,能够对接收到的模拟信号进行处理,实现信号放大,频率变换等功能,是各类通讯系统的重要组成部分,被广泛使用于宽带光通信、有线通信、有源铜缆、有源光缆等国家急需突破的科技领域。而在AFE中,Continuous Time Linear Equalizer(CTLE),即连续时间线性均衡器,是实现其功能的重要元件,能够补偿信道频带受限。

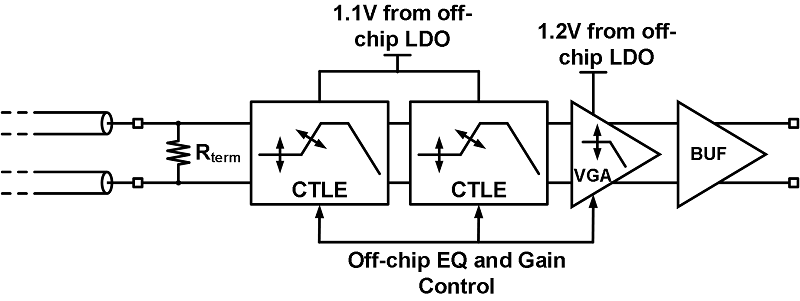

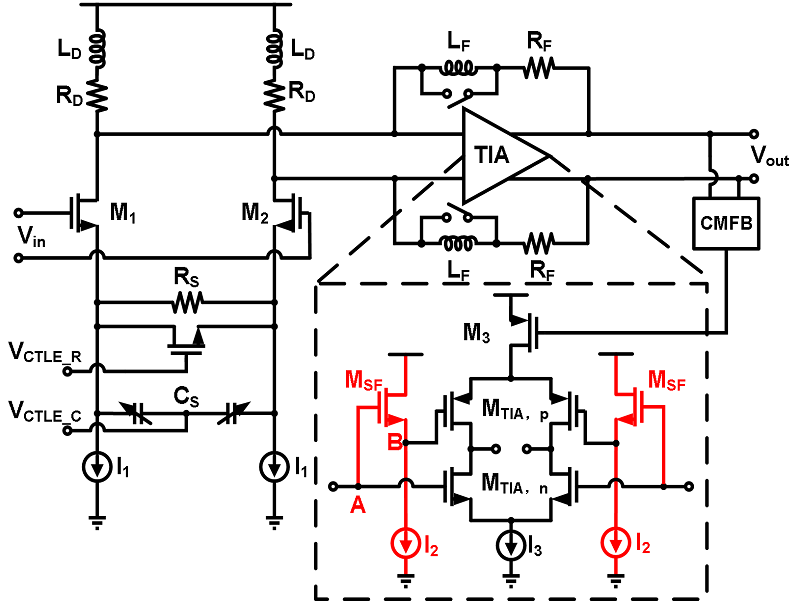

传统的均衡器,普遍具有在改变均衡能力时,其补偿频率也会随之改变,从而导致信号质量下降的问题。针对传统均衡器出现的问题,研究团队在论文[1]中提出新的AFE结构,通过同时控制均衡器以及可变增益放大器,可以实现固定的补偿频率,在直流增益、峰值增益和带宽之间进行了解耦。同时,研究团队在此工作中使用源极跟随器(SF)对传统的电路架构进行了改进,从而达到了更高的带宽。

图2 AFE体系结构图

图3 CTLE内部结构示意图

图4 56-Gb/s PAM4 眼图

本论文的核心思想,起源于潘权教授2015-2018年在硅谷创业公司工作期间,遇到的一个悬而未决的高速均衡技术难点。归国后,课题组招收的第一届本科生在潘权教授的悉心指导下,继续对此技术难点进行研究,从开设模拟集成电路课程开始,前后历时3年,依次完成了理论知识学习、技术难点分析、文献阅读、研究思路探索、电路架构探索、电路设计、流片验证、文章撰写和专业核心期刊投稿。该创新解决了传统均衡器普遍存在的均衡能力和系统带宽存在的矛盾,实现了均衡器在改变均衡能力时,能够固定补偿频率的功能。该技术的突破不仅填补了学术界的空白,更解决了工业界的实际问题。本论文获得了专业审稿人的一致好评。

本论文核心成员:

1. 李正浩,2016级南科大本科生,2020年进入南科大微电子学院攻读博士学位;

2. 唐敏哲,2016级南科大本科生,2020年进入日本东京工业大学攻读博士学位;

3. 樊泰扬,2016级南科大本科生,2020年进入南科大微电子学院攻读学术型硕士学位。

参考文献:

[1] Z. Li, M. Tang, T. Fan and Q. Pan, "A 56-Gb/s PAM4 Receiver Analog Front-End with Fixed Peaking Frequency and Bandwidth in 40-nm CMOS," in IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2021.3074384.

潘权课题组欢迎优秀的本科生、研究生和博士后加入。