当前位置 :首页>新闻动态

近日,南方科技大学微电子学院潘权课题组2020届本科毕业生在工学院综合设计中取得突出成果。李正浩、唐敏哲、樊泰扬、陆煜晨四位同学出色完成了与某知名通信公司合作的“面向下一代高速应用的低功耗SerDes前端芯片的研发”的项目。该项目采用TSMC 40nm CMOS工艺,设计了一款基于四电平脉冲幅度调制(4-Level Pulse Amplitude Modulation)传输方式的单通道56Gb/s高速SerDes模拟前端芯片。2020年5月芯片测试成功,在调节范围、信噪比等方面取得了优异的性能,同时还具备固定峰值频率和固定带宽等优点。此项目的研究工作成果得到合作企业高度认可,已成功转化成企业横向合作项目,以进一步深化企业和高校在高性能通信芯片的研究合作。

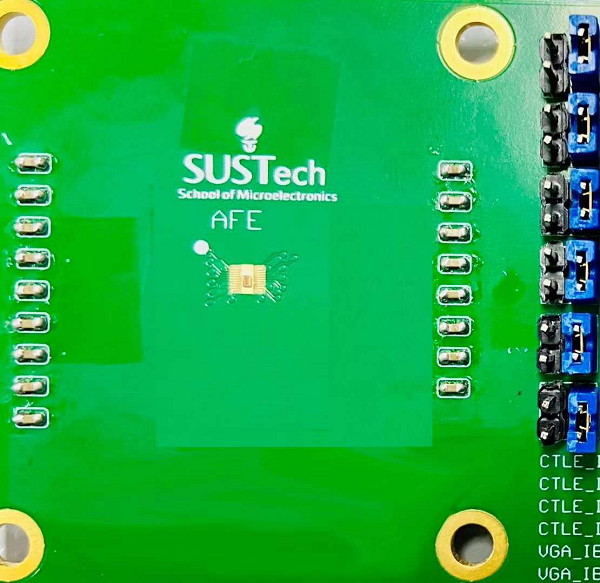

图1 (a)模拟前端电路PCB;

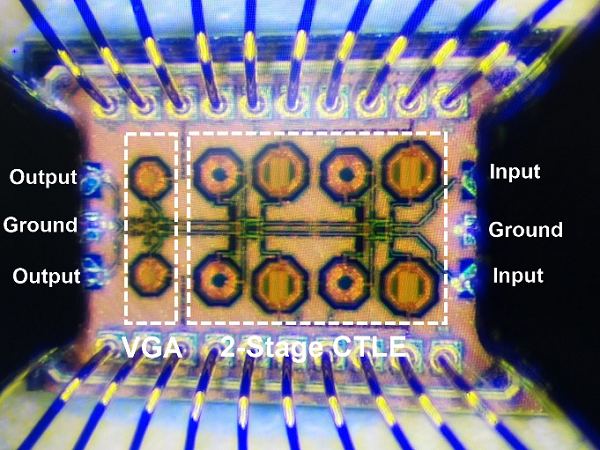

图1 (b)芯片显微图

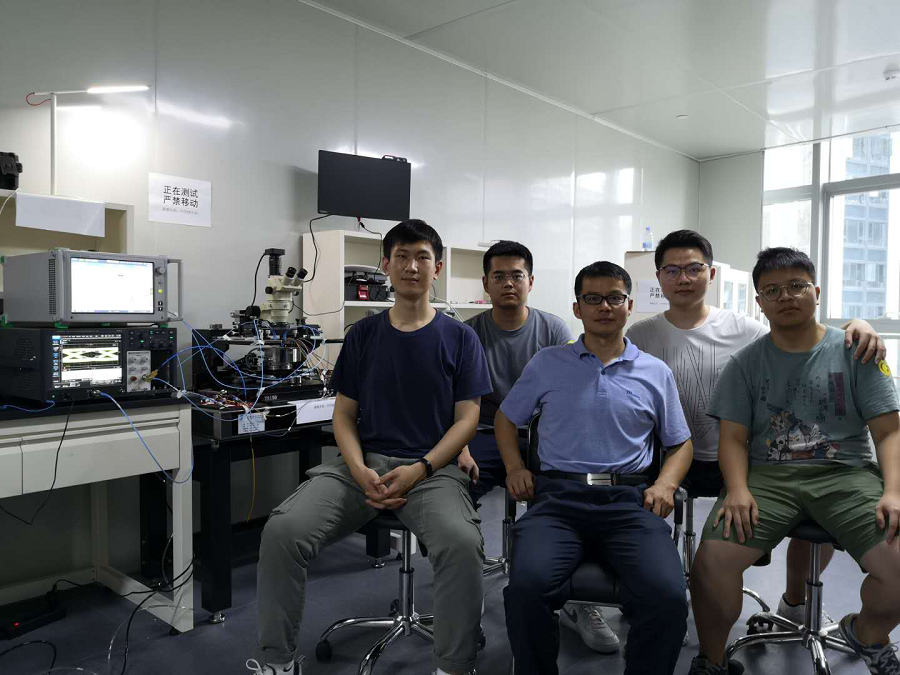

图2 综合设计小组合影,左起为李正浩、樊泰扬、潘权教授、陆煜晨、唐敏哲

高速串行通信因其节约传输媒介,降低系统互连复杂性,实现异步传输等诸多优点,越来越多地应用在网络传输、背板连接、I/O接口等领域。SerDes电路更是我国高性能集成电路领域中卡脖子的重要模块之一,目前国内市场上产品的速率仍以10G的芯片为主导。

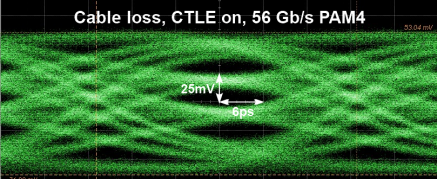

图3 56-Gb/s PAM4眼图

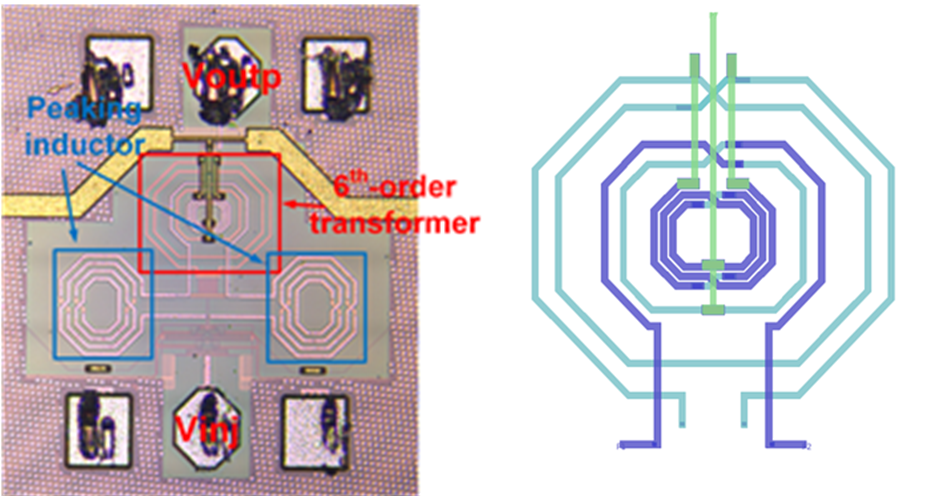

此外,该课题组2020届本科毕业生朱俊桦同学所设计的一款“基于变压器的注入锁频分频器”芯片,通过引入一个精心设计的片上变压器,扩大了锁定范围。2020年5月芯片测试成功,整体性能已达到世界领先水平。

图4 基于变压器的注入锁频分频器设计

图5 朱俊桦同学与潘权教授合影

潘权课题组2020届本科毕业生学术成果卓著,共计发表高水平会议论文2篇,申请电路发明专利2项,在投会议论文2篇,正在准备期刊论文2篇。课题组2020届8名本科毕业生全部顺利毕业,其中2名博士录取(东京工业大学/南方科技大学),4名硕士录取(代尔夫特大学/USCD/南科大/北航),2名参加工作。

潘权课题组欢迎优秀的本科生,研究生和博士后加入。

潘权教授课题组简介:潘权博士,主要研究工作集中在高速模拟/射频集成电路设计,主要包括:Wireline/Wireless高速通信集成电路(接收机/发射机)、Serdes/clock and data recovery(CDR)电路、低噪声放大器/频率综合器、硅光互连研究。潘权教授不仅在国际主流会议/期刊上发表多篇高水平学术论文,同时有超过8年丰富的国内外工作经验,包括4年硅谷业界最前沿的工作经验。

图6 潘权课题组合影