当前位置 :首页>新闻动态

近日,南方科技大学深港微电子学院林龙扬课题组分别在超低功耗集成电路设计和超低温集成电路设计取得新进展。相关成果:【论文1】“A 0.72nW, 0.006mm2 32kHz Crystal Oscillator with Adaptive Sub-Harmonic Pulse Injection from -40°C to 125°C in 22nm FDSOI”入选2024年VLSI Symposium,论文第一作者为2023级博士生朱英杰(深港微电子学院23届硕士毕业生);【论文2】“Bi-Voltage Scaling via Cryo-CMOS Standard-Cell Library and Fully-Automated Design for 34% Power Reduction and 1.5× DVFS Efficiency Improvement at 4K” 入选2024年ESSERC,论文第一作者为2022级硕士生吕浩然。

林龙扬助理教授为上述两篇论文的通讯作者,南方科技大学为上述两篇论文的第一单位,两篇论文都得到了国家自然科学基金和广东省基础与应用基础研究基金的支持。

论文1:0.72nW功耗、-40℃至125℃工作温度范围自适应次谐波脉冲注入式32kHz晶体振荡器 [1]

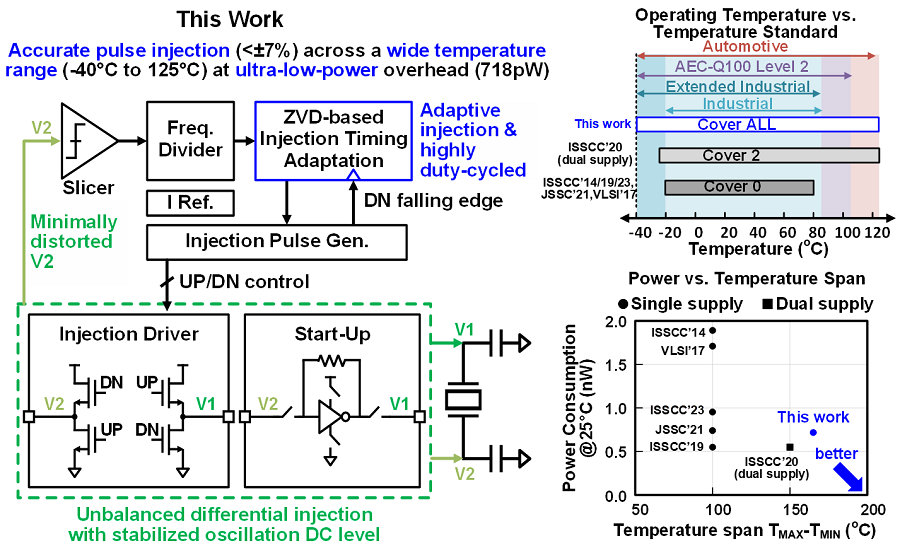

晶体振荡器 (XO) 在频繁循环的低功耗系统中执行关键的时间保持任务。它们需要在工艺、电压、温度(PVT)变化的影响下保持长期频率稳定性,并尽量减少功耗和面积开销。传统基于跨导gm单元的XO由于需要消耗静态偏置电流来维持振荡,导致功耗较大。基于脉冲注入的XO通过仅在振荡的峰值和谷值注入脉冲(能量),以获得最高的注入效率,从而实现更低的功耗。通过将脉冲注入频率降低到振荡频率的第N次谐波频率,可以实现亚纳瓦级的功耗。然而,一个关键的设计挑战在于脉冲注入的时序,这直接影响功耗、抖动和运行可靠性。随着谐波阶数N的增加(为了降低总体功耗),注入不准确性对性能下降的敏感度也会增加。此外,为了覆盖更广泛的工业和汽车应用,要求工作温度范围从-40°C到125°C,这对脉冲注入准确性的要求进一步提高,同时还需要尽量减少功耗和面积。基于开环注入时序控制的亚纳瓦XO受温度影响大,限制其工作温度范围。基于PLL的注入时序控制方法则需要消耗较大的功耗。本文提出了一种基于零电压检测的闭环时序控制电路,可以在PVT的影响下保证脉冲注入的准确性。该设计采用22-nm FDSOI工艺,仅占用0.006mm²面积,实现了0.72nW的超低功耗,艾伦偏差为11ppb,并且能在-40°C到125°C的温度范围内正常工作,是目前已发表的亚纳瓦XO中工作温度范围最广的设计。

论文2: 通过超低温CMOS标准单元库和全自动设计达到4K温区下34%功耗降低和1.5倍DVFS效率提升的双边压降方法 [2]

量子计算在解决传统计算机难以解决的复杂问题上有着广阔前景。对于超低温下量子比特的控制而言,工作在4K温区附近的超低温CMOS集成电路成为一种切实的解决方案,但其功耗被制冷机制冷功率严格限制。在超低温CMOS控制器中,数字部分的功耗占据主要,并且随着量子比特数目的不断增长,功耗问题将会日益严峻。

本论文通过利用CMOS晶体管在超低温下的高关断电压的特性,提出双边压降方案以充分利用4K温区下晶体管的压降潜力,从而大幅降低数字逻辑在超低温区的功耗。为适配双边压降方案,论文提出一种正常电压摆幅区间供电和双边压降区间摆幅供电逻辑门交替的电路结构,并且搭建一整套标准单元库,并通过全自动设计流程,在40nm工艺节点实现了超低温RISC-V子系统芯片。在4K温区下,相对于传统压降方式,双边压降取得34%功耗降低和1.5倍DVFS (Dynamic Voltage and Frequency Scaling, 动态电压频率调节)效率提升,这是首次利用超低温电压缩放潜力以最大化超低温数字系统DVFS效率的工作。

关于VLSI Symposium和ESSERC:

VLSI Symposium是与ISSCC、IEDM齐名的集成电路与半导体领域最高级别会议,每年都吸引着国际半导体业界和学术界的顶尖研究成果发表。该会议是由IEEE Solid-State Circuits Society, IEEE Electron Devices Society以及Japan Society of Applied Physics共同举办的高水平、高质量、高影响力的集成电路领域国际学术会议,每年轮流在美国和日本举办,汇集了来自工业界、学术界和政府机构的专家、学者参加,是展现和讨论集成电路与半导体领域前沿技术的重要平台,具有广泛的影响力。

ESSERC是European Solid-State Electronics Research Conference,即欧洲固态电子会议的简称,是过去ESSDERC-ESSCIRC会议的延续, 是固态电路和固态器件高水平顶级会议之一。ESSERC为来自全球范围内的众多专家学者和工业界研发人员提供了一个站在技术前沿与业界专家交流沟通的平台。

论文信息如下:

[1] Y. Zhu, Y. Lan, H. Li, H. Lyu, Z. Kong, J. Zhao, Y. Li, G. Wang, J. Li and L. Lin, "A 0.72nW, 0.006mm2 32kHz Crystal Oscillator with Adaptive Sub-Harmonic Pulse Injection from -40°C to 125°C in 22nm FDSOI ", 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024.

[2] H. Lyu, Z. Yang, B. Qiu, H. Li, Z. Kong, H. Yu, X. Wang, Y. Lan, Y. Zhu, S. Zhou, F. Zhou, K. Chen, J. Li, Y. Li, L. Lin, " Bi-Voltage Scaling via Cryo-CMOS Standard-Cell Library and Fully-Automated Design for 34% Power Reduction and 1.5× DVFS Efficiency Improvement at 4K ", 2024 European Solid-State Electronic Research Conference (ESSERC), Bruges, Belgium, 2024. (accepted)