当前位置 :首页>新闻动态

近日,我院潘权团队在高速集成电路设计领域取得重要进展,研究成果包括一款延迟锁相环芯片,一款VESEL发射机芯片,一款光电探测器以及一款低压降线性稳压器芯片。相关论文成果分别发表于IEEE Transactions on Microwave Theory and Techniques(TMTT),European Solid State Circuits Conference (ESSCIRC),IEEE Circuits and Systems Society期刊IEEE Transactions on Circuits and Systems II (TCAS-II)和European Conference on Optical Communications (ECOC)。TMTT和TCAS-II为芯片领域高水平学术期刊,ESSCIRC和ECOC为芯片领域顶级学术会议。

16相位高精度宽锁定范围的延迟锁相环

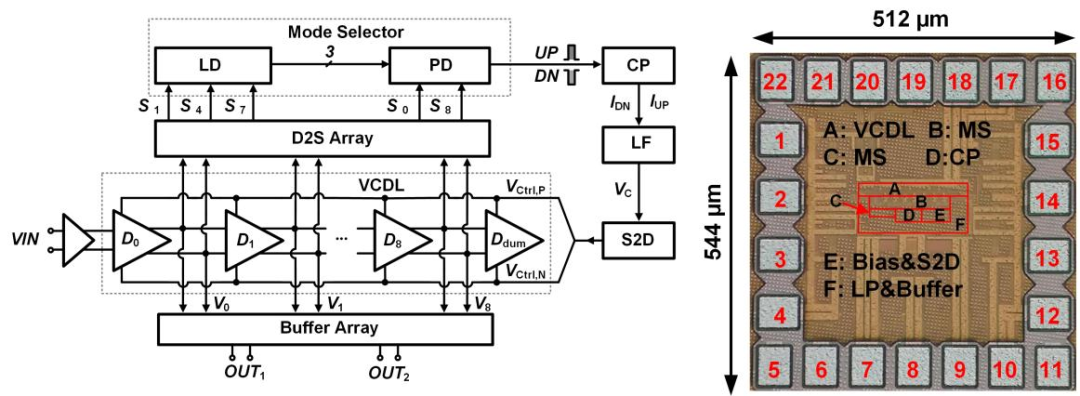

多相位时钟发生器广泛用于现代集成电路和系统。一组高相位精度时钟可提高时间交错型的模数转换器信噪比。基于高相位精度时钟的小数间隔前馈均衡发射机,在不放大噪声的情况下将补偿范围扩展到奈奎斯特频率之外,还保证了多路复用器中有足够的时序裕量。运用于四分之一速率时钟和数据恢复电路,则可以通过利用较低的恢复时钟频率来降低整体电路的功耗。作者采用了一种级联电流分流电荷泵和电流分割技术,有效抑制了16相输出中的电流失配和相位延迟误差,成功设计并验证了一种2.0-7.4 GHz 16相位的具有高相位精度和宽锁定范围的延迟锁相环。该成果以“A 2.0-to-7.4-GHZ 16-Phase Delay-locked Loop with a sub-0.6-ps Phase-Delay Error in 40-nm CMOS”为题发表。该论文提出的锁检测器解决了假锁定和谐波锁定问题,将检测范围从3/2输入时钟周期扩展到8/3时钟周期。其中,基于40nm CMOS工艺,提出的16相位的延迟锁定环在2.0 GHz时,相位延迟误差仅为0.50 ps(0.36°);在7.4 GHz时相位延迟误差仅为0.58 ps(1.55°)。芯片占用面积为0.0168 mm2,在7.4 GHz工作频率下,功耗仅为18.3 mW,对应功率效率高达0.15 mW/GHz/相位。

论文[1] 16相位延迟锁定环的原理框图(左)和芯片显微图(右)

论文[1] 工作在2.0/7.4GHz时的相位误差测试图(左)和假锁定自动纠正测试图(右)

南方科技大学和澳门大学联合培养的2019级博士生杨健为本论文第一作者,潘权教授为通讯作者。本工作得到了国家自然科学基金、广东省自然科学基金、深圳市科技计划和澳门特别行政区科技发展基金的支持。

[1] J. Yang, Q. Pan*, J. Yin and P. -I. Mak, “A 2.0-to-7.4-GHz 16-Phase Delay-Locked Loop With a Sub-0.6-ps Phase-Delay Error in 40-nm CMOS,” IEEE Transactions on Microwave Theory and Techniques, vol. 71, no. 8, pp. 3596-3604, Aug. 2023.

论文链接:https://ieeexplore.ieee.org/document/10043178/?arnumber=10043178

VCSEL发射机

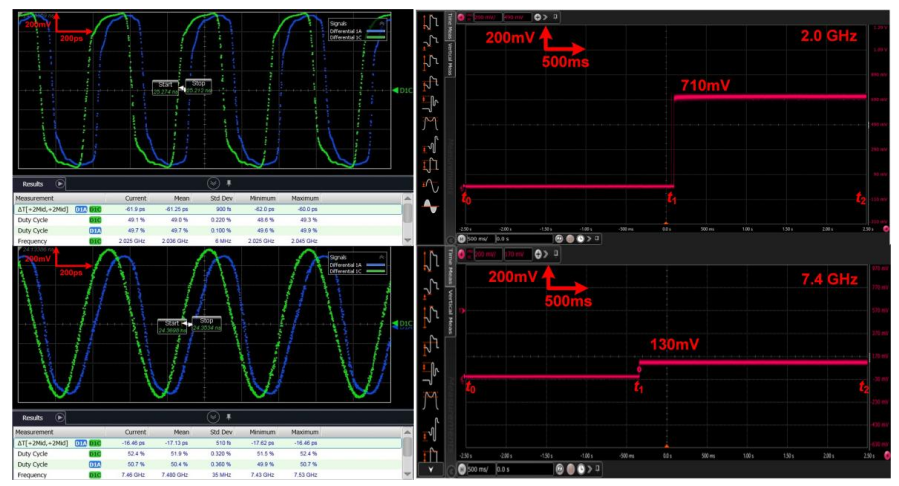

这项工作介绍了一种用于垂直腔面发射激光器(VCSELs)的40纳米CMOS技术的四分之一速率4级脉冲幅度调制(PAM-4)发射机。它采用了基于温度计编码的架构,配备有2级前馈均衡器(FFE),以独立控制顶部/中间/底部(T/M/B)数据片段的增益和均衡强度,并完全补偿VCSEL的非线性特性。此外,在连续时间线性均衡器(CTLE)内嵌了一种预加重电路,不仅可以减轻VCSEL对上升和下降过渡的不对称响应导致的数据眼偏斜,还可以扩展整体发射机带宽。光学测量结果表明,在56-Gb/s PAM-4数据速率和2.05-pJ/bit效率下,提出的分段非线性补偿方案将平均子眼高度/宽度和电平不匹配比(RLM)分别提高了14%/12%,而非对称均衡技术将水平电平眼偏斜降低了63%。

论文[2] Tx线与VCSEL连接的系统图及芯片测试结果

南科大-港科大联合培养博士生陈福栈为本文的第一作者,潘权教授为通讯作者。

[2] F. Chen, C. Zhang, L. Wang, Q. Pan and C. P. Yue, "A 2.05-pJ/b 56-Gb/s PAM-4 VCSEL Transmitter with Piecewise Nonlinearity Compensation and Asymmetric Equalization in 40-nm CMOS," ESSCIRC 2023- IEEE 49th European Solid State Circuits Conference (ESSCIRC), Lisbon, Portugal, 2023, pp. 373-376, doi: 10.1109/ESSCIRC59616.2023.10268794.

论文链接:https://ieeexplore.ieee.org/document/10268794

0.96–0.9-V的带有两级交叉耦合误差放大器的全集成的FVF LDO

全集成低压降稳压器(LDOs)在超大规模集成电路(VLSI)中由于设计成本低、占用面积小和电源抑制(PSR)能力好等特点而而具有吸引力。本工作应用在高速宽带通信系统中。

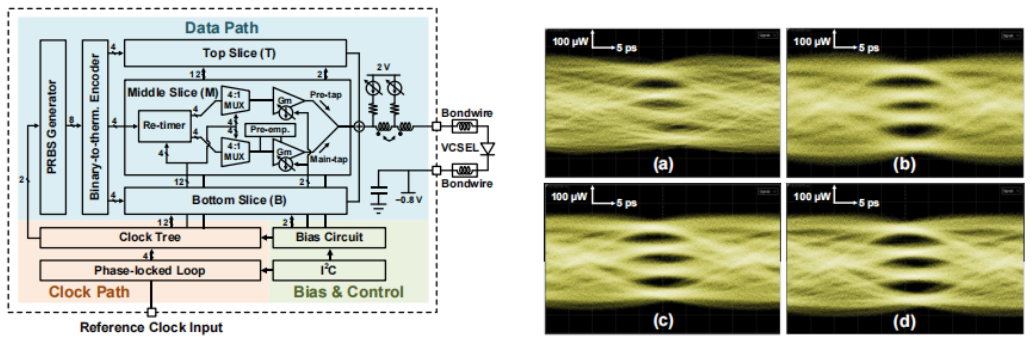

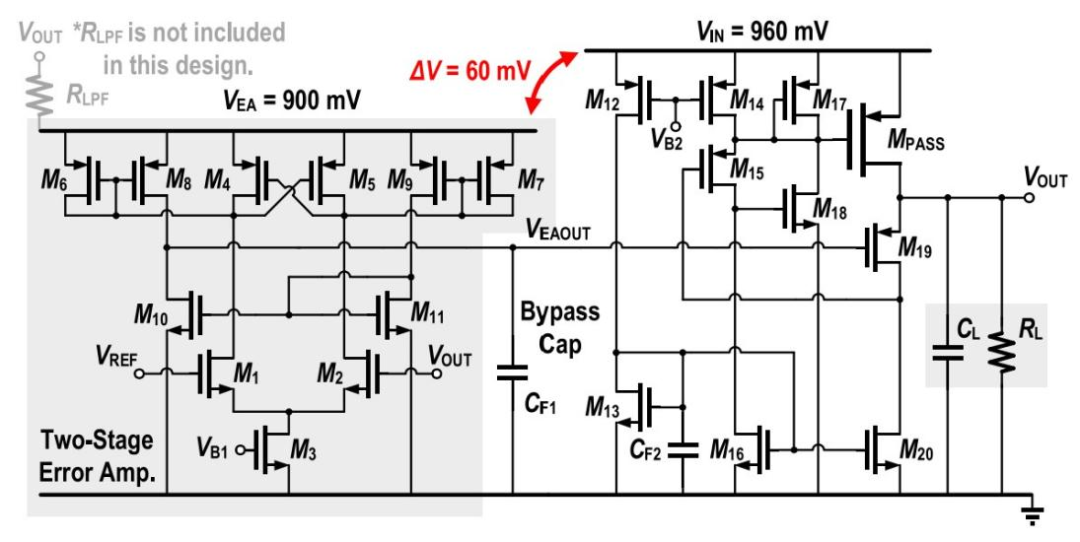

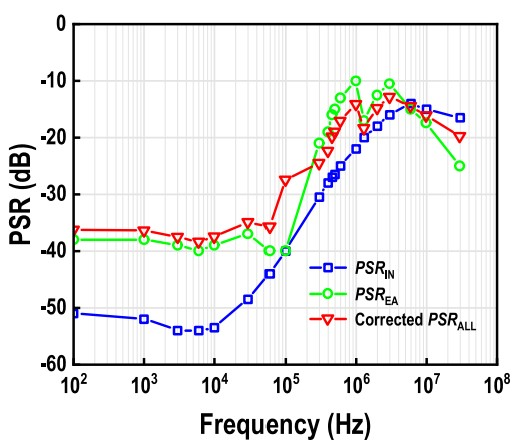

本文提出了一种具有高增益的两级交叉耦合误差放大器(XCEA)的基于翻转电压跟随器(FVF)的0.96–0.9-V全集成低压降稳压器(LDO)。所提出的XCEA结构克服了晶体管本征增益的约束,极大地提高了增益,并扩展了单位增益带宽(UGB),同时也实现了更好的电源纹波抑制能力(PSR),负载调节能力和更快速的响应能力。为了克服低压降对于输出端的功率P型MOS管(Mpass)负载能力的约束,并测定和评估PSR在不同回路中的性能,我们通过给功率晶体管和运算放大器(EA)分别提供不相等的电源电压,使得等效的压降增加,并可以分别测量PSR的不同部分。此外,在这个设计中还利用了滤波电容来提高稳定性和PSR。

所设计的LDO采用28nm体CMOS工艺,消耗135µA静态电流,占用0.0017 mm2的有源面积,在20mA负载下具有27MHz的单位增益带宽(UGB)。在CL = 200 pF的情况下,对于100 ps内从0mA升至20 mA的负载瞬态电流,所提出的LDO的响应时间为1.6ns,同时会伴有160mV的低冲。在所提出的高增益XCEA结构的帮助下,整体PSR在10 kHz时为-38dB,在30 MHz时为-20dB。LDO的功率效率为93.1%。

论文[3]中LDO在高速发射机中的典型工作场景

论文[3]中所提出的LDO晶体管级原理图

论文[3]中与分开的环路相比计算所得的PSR

南方科技大学潘权课题组科研助理徐东藩为本论文第一作者,潘权教授为通讯作者。

[3]D. Xu, Y. Zhang, X. Luo, Z. Li and Q. Pan*, "A 0.96–0.9-V Fully Integrated FVF LDO With Two-Stage Cross-Coupled Error Amplifier," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 10, pp. 3757-3761, Oct. 2023, doi: 10.1109/TCSII.2023.3292397.

https://ieeexplore.ieee.org/document/10173676

一种基于28-nm CMOS工艺渡越时间带宽增强型光电探测器

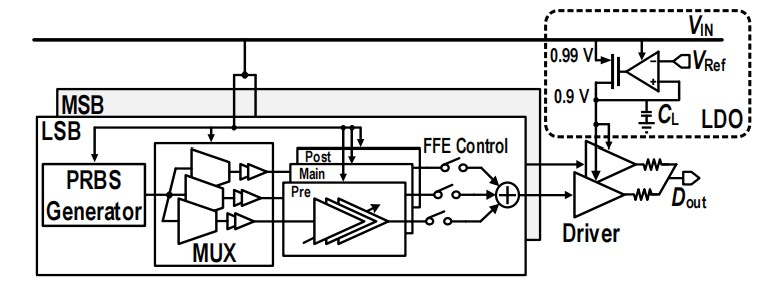

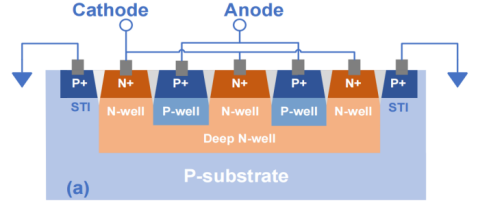

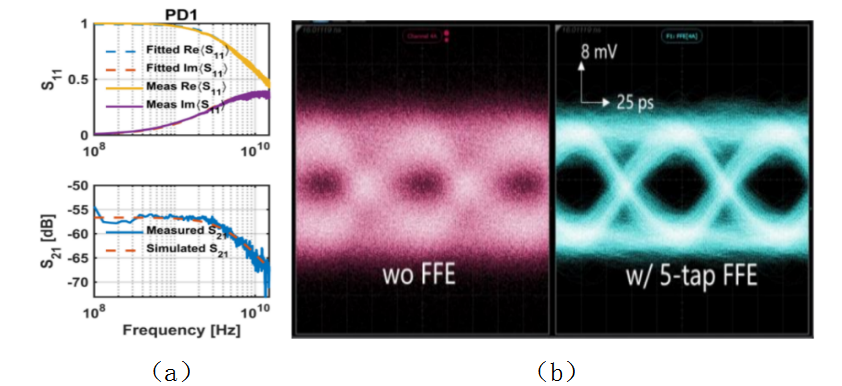

目前,短距高速光电通信系统面临两个难题,即接收端信号的带宽的不足和高速光电接收机的成本居高不下。高速光电探测器(Photodetector,PD)是光电接收机的重要组成部分,能够将光信号转换为电流信号。相比于采用Ge等元素制造的片外PD,基于CMOS标准工艺的PD能够实现封装成本的大幅度降低,并且可以与接收机电路集成在同一块芯片上,实现全集成的光电接收机,但带宽仍然是限制其发展的最关键的问题。CMOS PD的带宽主要受光生载流子的渡越时间和PN结RC参数的限制,在接收机电路中通过利用前置和后置均衡技术,如前馈均衡器(FFE)、连续时间线性均衡器(CTLE)和判决反馈均衡器(DFE),能够有效改善RC带宽。然而,很少有报道CMOS PD的传输时间带宽的改善。

论文提出了一种在标准CMOS中制备的渡越时间带宽增强型PD。该光电探测器通过设置交错的P/N阱构成横向PN结,在接入反偏电压后能够为光生载流子提供较强的横向电场以加速载流子的运动。该PD在850-nm光的测试中实现了0.13-A/W的响应率和10.43GHz的渡越时间带宽。此外,将10Gb/s数据率的光信号直接输入给该PD,能够获得的非常清晰的光学眼图。

论文[4]横向叉指增强型PW/DNW PD

论文[4](a)PD的s参数测试和仿真(b)光学测试中PD的10Gb/s输出眼图

南方科技大学博士后周德为本论文第一作者,潘权教授为通讯作者。本工作得到了国家自然科学基金、广东省自然科学基金、深圳市科技计划的支持。

[4] D. Zhou, H. Wang, D. Zhan, Q. Pan, "Transit-time Enhanced Silicon Photodetector with Lateral lnterleaved P-well/N-well Junction in 28-nm CMOS Technology," in European Conference on Optical Communications (ECOC), 2023.