当前位置 :首页>新闻动态

近日,国际固态电路大会(ISSCC 2024)在美国旧金山举行。ISSCC (International Solid- State Circuits Conference) 国际固态电路会议由IEEE固态电路学会(SSCS)举办,是世界学术界和工业界公认的集成电路设计领域最高级别会议,被认为是集成电路设计领域的“芯片奥林匹克大会”。始于1953年的ISSCC通常是各个时期国际上最尖端固态电路技术最先发表之地。每年吸引超过3000名来自世界各地工业界和学术界的参会者。据报导,中国从2005年首次在ISSCC发表论文以来,截止ISSCC 2024,一共发表206篇论文。

ISSCC每篇论文都代表着当前芯片领域最前沿的研究成果。南方科技大学微电子学院今年共有3篇论文入选,全部来自于潘权教授团队。其中,高速有线通信方向2篇:论文1“A 112Gb/s/pin Single-Ended Crosstalk-Cancellation Transceiver with 31dB Loss Compensation in 28nm CMOS”,论文2“A 224Gb/s/wire Single-Ended PAM-4 Transceiver Front-End with 29dB Equalization for 800GbE/1.6TbE”。高密度存储器和接口方向 1篇:“A 64Gb/s/pin Single-Ended PAM-4 Transmitter with a Merged Pre-Emphasis Capacitive-Peaking Crosstalk Cancellation Scheme for Memory Interfaces in 28nm CMOS”。

潘权和三位会议报告学生(钟立平,伍伟涛,罗雄师-2019届南科大本科毕业生)合影

在高速有线通信方向,目前北美企业保持优势。2024年整个session共收录13篇论文,其中有9篇来自北美区(Intel, Marvell, Synopsys等清一色顶尖科技公司)。中国大陆今年仅有2篇有线通信的论文,全部来自南科大潘权团队。迄今为止,中国大陆也仅北京大学和南方科技大学有本领域的ISSCC成果发表。

在高密度存储器和接口方向,目前韩国和美国企业保持领先。2024年整个session共收录10篇论文,其中8篇来自韩国和美国公司(SK Hynix,三星,美光),1篇来自韩国Kwangwoon大学,1篇来自南科大潘权团队。据报导,这是中国大陆在ISSCC高密度存储器和接口方向有史以来的首篇论文。

ISSCC 2024会议现场

论文一: 112Gb/s/pin Single-Ended Crosstalk-Cancellation Transceiver with 31dB Loss Compensation in 28nm CMOS

云计算和人工智能等应用的发展,将数据中心的高速接口推向了更高的数据速率,目前超高速有线收发机的数据速率正迫切需要推动到200+Gb/s量级。然而,这个数据速率对无源组件(如连接器、信道和封装)的信号完整性提出了更严格的要求。单端方案可能是数据速率的实用且经济高效的解决方案。首先,它通过一个差分信道传输两路单端信号,使吞吐密度翻倍。此外,该方案还放松了对无源组件的奈奎斯特带宽要求。但是,单端链路遭受了更严重的噪声,特别是长距(LR),中距(MR)和超短距(VSR)链路中引入的串扰噪声。

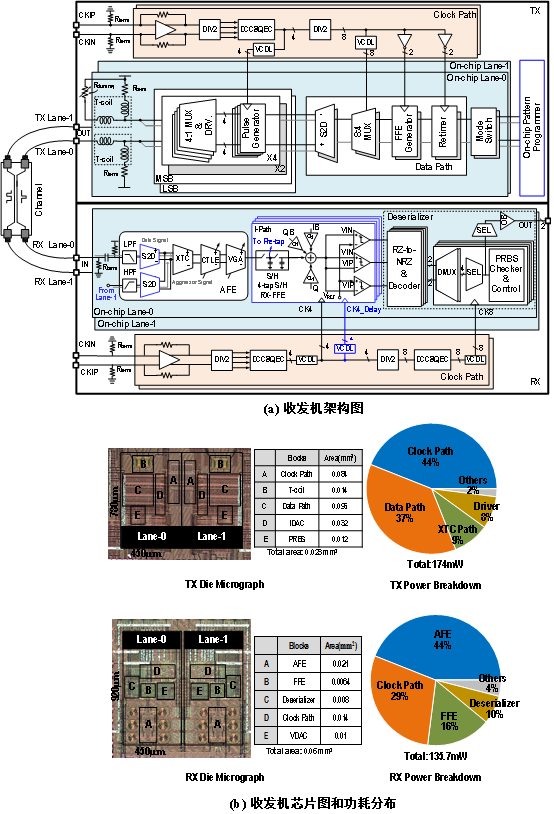

南方科技大学潘权教授团队从系统架构和电路设计入手,针对复杂的信道环境引入的串扰问题,在发射机中提出可重构串扰消除技术来灵活地处理轻度的感性串扰噪声和容性串扰噪声,接收机采用低功耗的MIMO串扰消除技术处理严重的感性串扰噪声。为了抑制单端电路中的电源噪声等,在接收机侧的第一级使用伪差分架构抑制噪声,后续所有级使用全差分电路架构。为了缓解伪差分失配和提升带宽,该工作提出了Gm-TIA型的单端转差分转换器,使用强弱路径相加和非对称有源电感技术实现优秀的伪差分失配缓解和带宽提升。此外,为了在基于相对落后的28nm CMOS工艺上实现112Gb/s的数据速率,基于多相位时钟技术的接收机侧FFE提出以消除ISI并实现低功耗。

基于上述创新设计,该工作提出了一款基于28nm CMOS工艺的超高速单端串扰消除收发机,并进行了测试验证。该芯片在一对差分信道实现了2×112Gb/s,功率效率为2.77pJ/b(发射机为1.56pJ/b,接收机为1.21pJ/b)。它展示了未来800G/1.6T以太网中具有成本效益的解决方案的潜力。

该工作以《112Gb/s/pin Single-Ended Crosstalk-Cancellation Transceiver with 31dB Loss Compensation in 28nm CMOS》为题发表于ISSCC 2024年的超高速有线专题。

论文二: A 224Gb/s/wire Single-Ended PAM-4 Transceiver Front-End with 29dB Equalization for 800GbE/1.6TbE

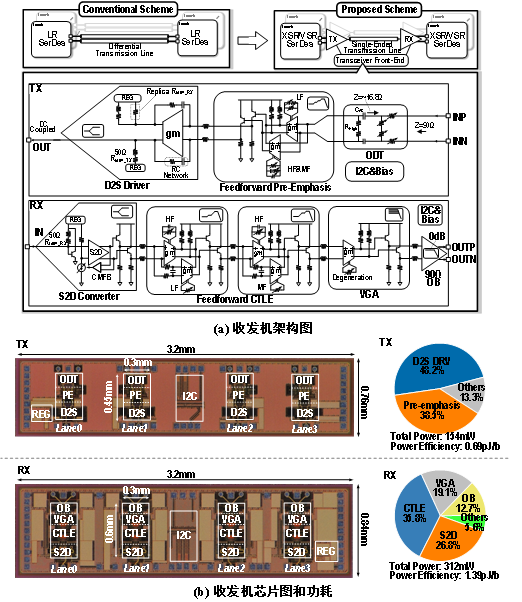

随着全球数据流量吞吐的指数增长,数据中心交换机系统的带宽容量在过去12年里增加了80倍。目前,交换机高速接口要求高速收发机的速率达到每通道224Gb/s。针对224G链路长距高损耗场景下高能效、高密度、低延迟的需求,目前讨论的可能方案有:基于高阶电平调制(PAM6/PAM8)方案、基于DSP的方案、长链路插入中继器方案等,但这些方案大部分存在电路系统复杂庞大、能耗较大、延迟高且难以实现高密度的问题。

该论文首次提出了基于“XSR/VSR SerDes或retimer+单端收发前端”的长距链路方案,此方案利用单端收发前端实现了高能效和低延迟的损耗补偿和传输距离拓展。此外,发射机和接收机前端电路的连接是基于高密度的单端传输线阵列,这可以帮助实现高密度的布线难题。收发机前端使用了直接耦合的设计,避免了使用大面积的片上或片外隔直电容以支持高密度的Pin口和传输线布局。收发机前端基于高共模抑制的差分和伪差分电路设计,改善单端链路对电源噪声敏感的问题。收发机前端设计了低频/中频/高频的均衡,在不同的损耗场景下均可获得平整的链路响应。发射机和接收机前端分别引入了群时延和电源反弹消除技术。收发机前端选取了SiGe工艺进行设计,充分利用SiGe工艺高增益、低噪声、高摆幅范围的特点以实现高均衡能力、高SNR、高线性度。

基于上述创新设计,此工作提出了一款基于130nm SiGe工艺的4通道高速单端收发机,并完成了测试验证。此电路在224Gb/s/wire速率下可以实现最高补偿29dB损耗,FOM(能效/损耗)值为0.07pJ/b/dB,误码率低至1E-7。

该工作以《A 224Gb/s/wire Single-Ended PAM-4 Transceiver Front-End with 29dB Equalization for 800GbE/1.6TbE》为题发表于ISSCC 2024年的超高速有线专题。

论文三: A 64-Gb/s/pin PAM4 Single-Ended Transmitter with Merged Pre-Emphasis Capacitive-Peaking Crosstalk Cancellation for Memory Interfaces in 28nm CMOS

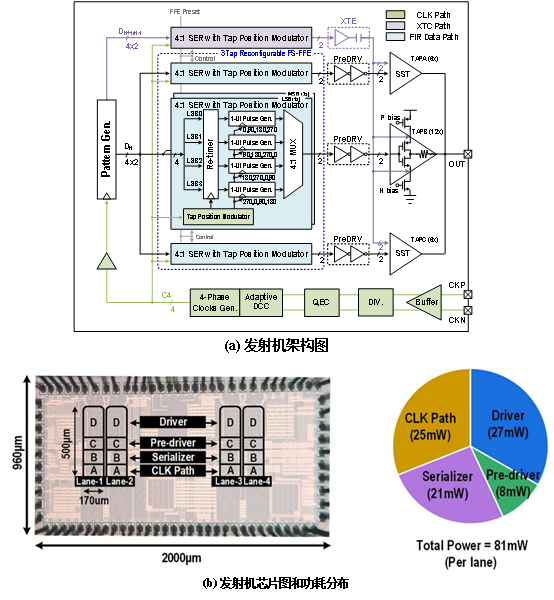

随着海量计算和人工智能应用的发展,对内存接口的数据吞吐量要求不断提高。影响内存接口吞吐量的两个关键指标分别是单通道数据率和通道密度,随着通道间距的减少,串扰导致的信号完整性问题愈发严重,严重限制了通道密度和数据吞吐量的提高,并且GDDR6X等先进DRAM应用已经采用PAM-4信令来提高数据传输速率,PAM-4信号对串扰的敏感性更会加剧这一问题。虽然已经报道了一些发射机串扰消除技术,但这些技术主要集中在NRZ,且存在信噪比低、接口效率低或能耗高的缺点。因此,非常需要一种同时兼顾高信噪比、高接口效率和低功耗的PAM-4串扰消除技术。

该论文提出了一种集成型预加重电容-峰化串扰消除技术,采用电容阵列生成串扰消除信号不降低输出摆幅,该电路集成在驱动器内部避免发射机输出节点的寄生堆积,支持高速率运行。发射机串行器采用动态逻辑门以减小寄生、提高带宽;采用无静态电流的反相器型数据选择器以降低功耗开销;采用抽头位置调制器通过时钟相位调制实现可重构的3抽头分数间隔前馈均衡,可根据信道特性定制化抽头顺序,并提供超奈奎斯特频率的补偿范围,从而进一步拓展带宽和PAM-4眼图的水平眼宽。此外,在时钟路径上,采用自适应占空比校正器和正交误差校正器消除时钟的偏斜,减少输出抖动。

基于上述创新设计,此工作提出了一款基于28nm CMOS工艺的4通道高速PAM-4单端串扰消除发射机,并完成了测试验证。与先前已发表的单端存储器发射机接口相比,本工作实现了最高的数据率64Gb/s/pin,功率效率为1.27pJ/bit,同时达到了82%的串扰引入抖动消除率。

该工作以《A 64-Gb/s/pin PAM4 Single-Ended Transmitter with Merged Pre-Emphasis Capacitive-Peaking Crosstalk Cancellation for Memory Interfaces in 28nm CMOS》为题发表于ISSCC 2024年的高密度存储器与接口专题,为中国内地在ISSCC该专题实现了论文零的突破。

这三项工作得到了国家自然科学基金和国家重点研发计划的支持。

除此之外,潘权教授团队在过去一年中,在高速通信芯片领域还有三篇CICC (1、 A 128Gb/s PAM-4 Transmitter with Edge-Boosting Pulse Generator and Pre-Emphasis Asymmetric Fractional-Spaced FFE in 28nm CMOS; 2、A 6.0-to-6.9GHz 99fsrms-Jitter Type-II Sampling PLL with Automatic Frequency and Phase Calibration Method Achieving 0.62μs Locking Time in 28nm CMOS;3、 A 56-Gbaud 7.3-Vppd Linear Modulator Transmitter with AMUX-based Re-configurable FFE and Dynamic Triple-stacked Driver in 130-nm SiGe BiCMOS),一篇ESSCIRC (A 2.05-pJ/b 56-Gb/s PAM-4 VCSEL Transmitter with Piecewise Nonlinearity Compensation and Asymmetric Equalization in 40-nm CMOS),一篇ASSCC (A 2x24Gb/s Single-Ended Transceiver with Channel-Independent Encoder-Based Crosstalk Cancellation in 28nm CMOS)等高水平会议论文被接收。