current location :home>News

Known as the “mother of chips”, Electronic Design Automation (EDA) tools go through the entire flow of design and manufacture of integrated circuits (ICs), covering the modeling and simulation of semiconductor devices, circuit simulation, logic synthesis, placement & routing, and many other steps. It is an indispensable part of the modern chip industry and a critical weak link in China’s IC industry, where oversea vendors occupy over 90% of markets.

As an essential segment of the EDA toolchain, the modeling and simulation of semiconductor processes and devices, also known as computer-aided design technology (TCAD), refers to using numerical methods and computer simulation to predict the characteristics and behaviors of semiconductor devices. They provide valuable information for design and manufacturing optimization.

In the meantime, circuit simulation is one of the most widely used EDA tools. However, the increasing complexity of IC design constantly challenges the current mainstream circuit simulation framework SPICE, whose performance lags behind the industrial need. Therefore, circuit simulation has become one of the major bottlenecks in the current EDA flow.

Assistant Professor Quan Chen’s research team from the School of Microelectronics at the Southern University of Science and Technology (SUSTech) recently made advancements in multi-physics modeling of the Spin-Transfer-Torque MRAM (STT-MRAM) devices and acceleration techniques for power/ground networks analysis.

Their works have been accepted by the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (IEEE TCAD) and the 2022 International Conference on Computer-Aided Design (ICCAD 2022), a top-tier journal and conference in the EDA domain.

The first paper, entitled “TEMT: A Transient Electronic-Magnetic-Thermal Coupled Simulation Framework for STT-MTJs,” was published in IEEE TCAD. This study proposes a fully coupled, transient electronic-magnetic-thermal (TEMT) modeling approach for STT-MTJ devices.

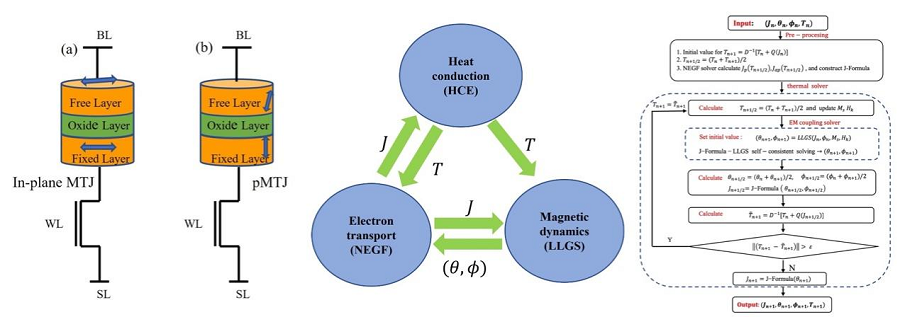

An STT-MRAM is a typical spintronics device that stores the 0/1 bit through the magnetic-resistance effect of the magnetic tunneling junction (MTJ) and writes the information via the spin transfer torque of the tunneling electrons (Figure 1, left). The write operation of STT-MRAM involves three primary physical processes: electrical (spin-polarized electrons transport), magnetic (magnetic dynamics), and thermal (thermal dynamics), along with the complex non-linear interactions among them (Figure 1).

Figure 1. 1T-1R STT-MRAM, which consists of a transistor and an MTJ (left); The three primary physics and their mutual coupling in the write operation of the device (middle); TEMT simulation framework for the device (right)

However, due to the difficulty and high computational complexity of the multi-physics modeling, the state-of-the-art commercial tools only allow the coupling of one or two physics processes in the TCAD modeling of the STT-MRAM, especially in the transient analysis. Such shortcoming inevitably results in insufficient simulation accuracy and limited capability to guide practical design and optimization.

In this project, the researchers proposed, for the first time, an efficient multi-physics coupling simulation framework for STT-MRAM that combines all three physical processes. The non-equilibrium Green’s function method (NEGF), the macro-magnetic dynamic equation (LLGS), and the heat conduction equation (HCE) are coupled and solved by a two-layer self-consistent iterative and implicit solution scheme, as shown in Figure 1 (right).

At each time point, two NEGF solutions are conducted to obtain the current densities corresponding to the two representative states of the MTJ, from which an approximated resistance formula is derived and used in subsequent electro-magnetic iterations. This largely reduces the number of expensive NEGF solutions in the entire simulation process (~15X) without compromising accuracy.

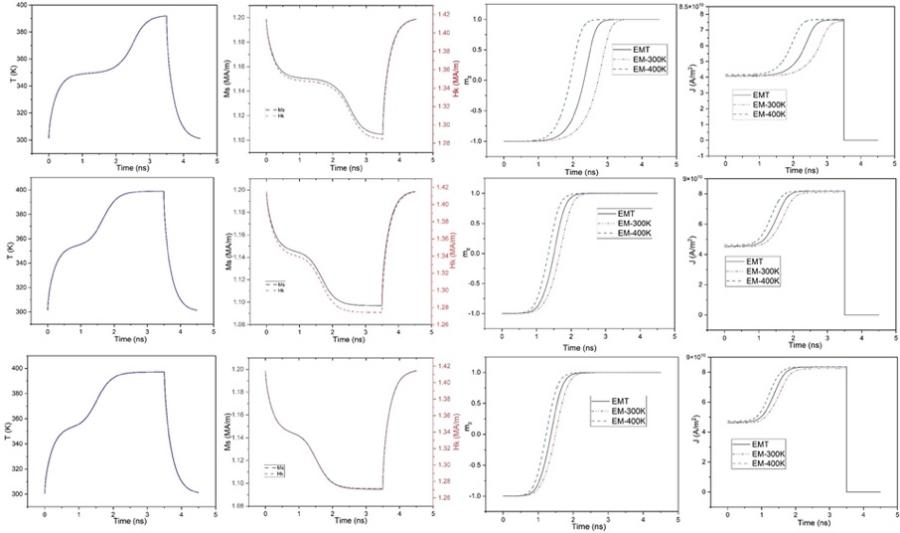

The proposed TEMT framework is the first simulation framework in the literature that can model the complete couplings among the three processes for STT-MRAM in the time domain while maintaining industrially feasible performance. Using this framework, Prof. Chen’s team studied the dynamic flipping characteristics of devices with different cross-sectional dimensions, as shown in Figure 2. The simulation results suggest that a larger lateral size increases the tunneling current density, resulting in a faster temperature rise and a shorter turnover time, which is consistent with the existing experimental results.

Figure 2. From up to down: with a 0.5V applied bias, the simulated transient results of physical parameters (temperature, magnetization, magnetization orientation, current density) of the device with different cross scale (10nm, 30nm, 60nm)

Dawei Liu, a Ph.D. student from the School of Microelectronics at SUSTech, is the first author of this paper. Asst. Prof. Quan Chen is the corresponding author, while SUSTech is the first affiliation.

This work was supported by the Key Program of the National Natural Science Foundation of China (NSFC).

The second paper, entitled “EI-MOR: A Hybrid Exponential Integrator and Model Order Reduction Approach for Transient Power/Ground Network Analysis,” was accepted by ICCAD 2022, a premier forum that explores new challenges, presents leading-edge innovative solutions, and identifies emerging technologies in electronic design automation research areas.

Post-layout simulation is one of the critical tasks in modern IC design. The size of post-layout simulation grows rapidly with the advancement of Moore’s Law, especially the Power/ground (P/G) network simulation, where millions to billions of unknowns are common. Full-chip post-layout simulations at advanced nodes easily consume weeks of verification time, rendering circuit simulation a major productivity bottleneck in the current EDA flow. Acceleration techniques are therefore pressingly demanded to meet the ever-increasing need for circuit simulation capability and scalability.

To address these issues, Prof. Chen’s group focused on Model Order Reduction (MOR) and Exponential Integrator (EI), two mainstream acceleration methods. They proved mathematically that EI could be viewed as a series of moment-matching MOR. It applies a simplified MOR in each time step based on a rational Krylov subspace with a single input, then advances the reduced system using the EI approach in the same step. It is the first rigorous proof that links these two research domains that have long been considered independent.

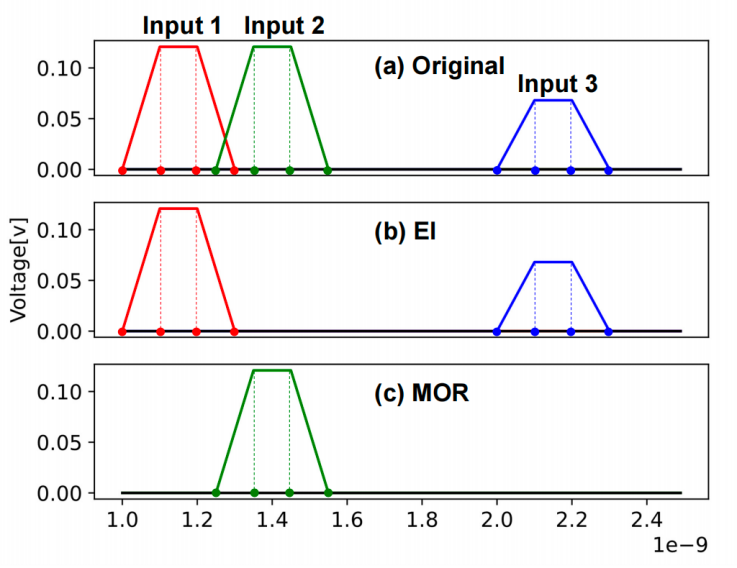

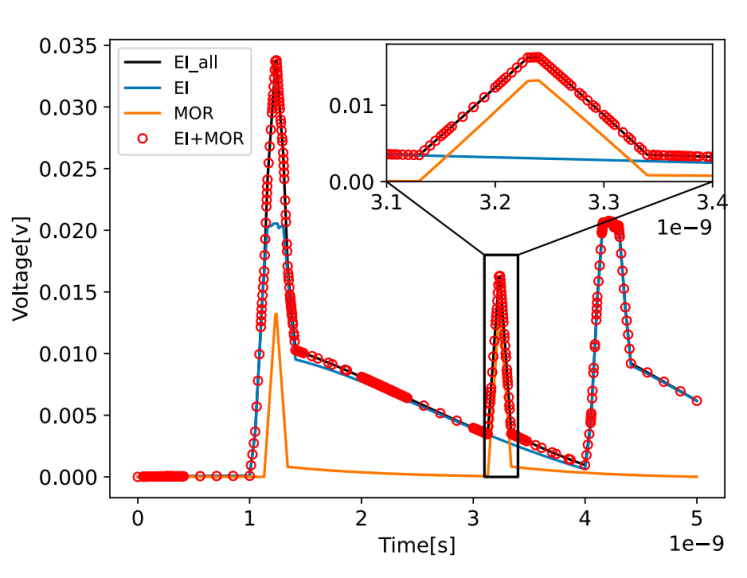

Motivated by the equivalence, the researchers designed a hybrid method EI-MOR to tackle the input misalignment problem in EI for transient P/G network simulation. The method divides the inputs into a majority group of well-aligned inputs and a minority group of misaligned inputs (Figure 3). EI handles the well-aligned group as usual. MOR treats the misaligned one to produce an input-independent reduced order model (ROM) whose simulation cost is not sensitive to the number of time points. The EI and MOR solutions are then superimposed to generate the final solution at the required time points (Figure 4).

Figure 3. Illustration of input grouping

Figure 4. Transient waveform of EI-MOR

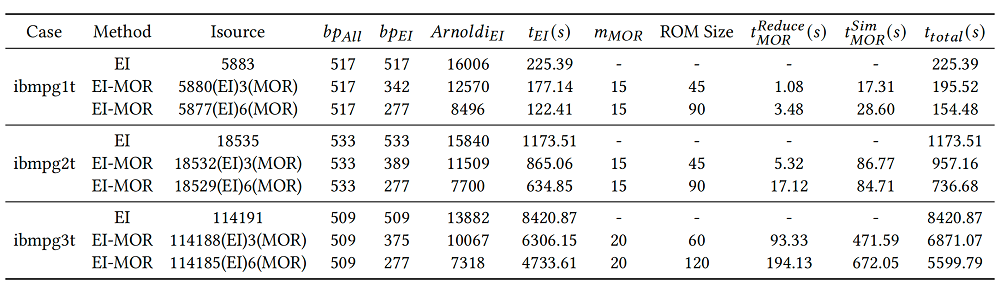

According to the numerical experiments in a Python-based simulator Ahkab, they confirmed the equivalence between EI and MOR. Moreover, it is evident from Table 1 that the proposed hybrid EI-MOR scheme is as accurate as the original solution. Importantly, this equivalence also provides new sights to bridge the two separate domains of EI and MOR, hopefully facilitating further understanding and development in transient circuit simulation.

Table 1. EI-MOR Performance

Cong Wang and Dongen Yang, master’s students from the School of Microelectronics at SUSTech, are this paper’s first and second authors. Asst. Prof. Quan Chen is the corresponding author, while SUSTech is the first affiliation.

This work was supported by the Special Funds of the National Natural Science Foundation of China (NSFC) and the Key Area Research and Development Program of Guangdong Province.

It is worth noting that this is the first time a paper from SUSTech has been accepted at the International Conference on Computer-Aided Design. This conference, along with the Design Automation Conference (DAC), and the Design, Automation and Test in Europe Conference (DATE), are the three top international conferences in the field of EDA. They are recommended by the China Computer Federation (CCF) as the top international conferences in the area of computer architecture and high-performance computing. ICCAD 2022’s acceptance rate is only 23% and will be held on October 30 in San Diego, California, USA.

Related links:

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems paper link: https://ieeexplore.ieee.org/document/9877863

2022 International Conference on Computer-Aided Design conference link: https://iccad.com/